Design and Implementation of High Performance and Low Power Mixed Logic Line Decoders

Full text

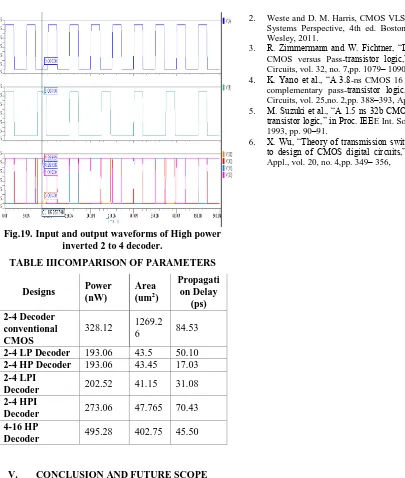

Figure

Related documents

[1]Stakhov A.,The golden section and modern harmony mathematics, Application of Fibonacci numbers, Vol. [2]De Villiers, M.,A Fibonacci generalization and its dual,

Therefore, from the issues stated above, this study is to identify what are the circumstances that brings the parties to litigation regarding Variation Orders in Lump

maximum N recycling back to the belowground systems, thus decreasing the requirement for external N inputs. In contrast, the two-cut harvest system removed excessive N but did not

Table 4.21: Density, Kinematic Viscosity, and Absolute Viscosity-Composition Data for the Binary System: Toluene (1) + Ethylbenzene

Wang et al Virology Journal 2012, 9 127 http //www virologyj com/content/9/1/127 RESEARCH Open Access Protective efficacy of a broadly cross reactive swine influenza DNA vaccine encoding

Hindawi Publishing Corporation EURASIP Journal on Wireless Communications and Networking Volume 2006, Article ID 78954, Pages 1?9 DOI 10 1155/WCN/2006/78954 Exploiting Diversity for

Given a set of resources to which a user has access and at least a small set of job requirements, the third step in the resource discovery phase is to filter out the

Based on the previews study a comparative study on PCR for flexible roads, the data that is gathered for 50 lanes of urban roads (flexible pavements) is further analysed