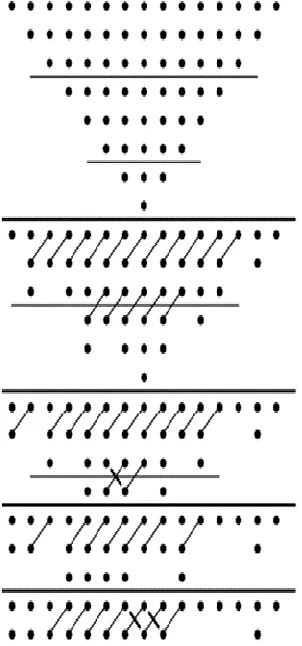

Efficient Framework For Column Reduction Multiplier In Vlsi Applications

Full text

Figure

Related documents

A study on high school football players measured number of impacts to the head and. neurophysiologic function with

Keywords: Handwriting recognition, parametric curve, implicit curve, orthogonal bases, critical points, Chebyshev basis, Legendre basis, resultants, resultants in orthogonal

More specifically, we operated on three distinct datasets: a first set of 24 digitally acquired cases on a GE Senograph 2000D containing 98 images (characteristics: size

When the circumstances of the competition lead to the arrival of big groups at the transition area, the time lost in T2 can be increased for those triathletes arriving in the

In [7] author described a method in which cryptography, steganography and parallelization were used altogether for data hiding, encryption was done using XORing of message

Assessment of current environmental pollution caused by the seagoing vessel, the situation of waste management at Vietnamese seaports and the extent to which

Although column-oriented database concept of column-by-column storage of columnar databases and columnar extensions to row-based databases, in NoSQL column-oriented stores, do