Title: An Improved Implementation of 4-bit Multiplier Using Reversible Gates

Full text

Figure

Related documents

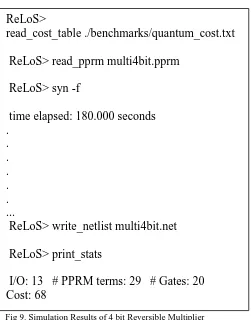

Such a reconfigurable gate gates built from standard reversible, which means that the design, CNOT, Toffoli and Friedkin has been submitted to the gates.. Simulation and

The proposed Urdhva Tiryakbhayam Vedic multipliers using reversible logic gates is improved by reducing the total number of gates, garbage outputs, quantum cost and Total

The particular function like Binary Subtraction is implemented using TR gate effectively by reducing number of Reversible gates, Garbage outputs and Quantum Cost.. Thapliyal

The proposed Design consists of Multiplier and Divider circuits of Low Power dissipation using Reversible logic gates and High Speed Using Vedic Mathematics..

There are many number of reversible logic gates that exist at present. The quantum cost of each reversible logic gate is an important optimization parameter [16]. The

With the inference of this paper, it is proved that full adder, reversible 4:2 compressor and the multiplier architectures designed using the TSG gate are beneficial than

The 32x32 bit vedic multiplier is designed by using reversible logic gates like Feynman gate, Peres gate, HNG gates and four 16x16 bit vedic multipliers.. Similarly divider

In the proposed design this gate is used to copy the operand bits and it is shown that the number of gates required to copy is reduced by 50% with same quantum cost.. Of all this