Techniques for Low Power and Area Optimized VLSI Testing using Novel Scan Flip Flop

Full text

Figure

Related documents

-the consequence of a partial ban = children may all move to the sector which is not banned, and thus child labor would not be eradicated..?. -Set up the di ff erence in di ff

Since then his research has looked at the role and infl uence of transnational non-state actors in transatlantic relations, and he has published widely on these topics in

Drawing upon Walt and Gilson ’ s policy analysis framework, this paper explores the tension between public policy and religious dogma for the strategies chosen by the Ethiopian

Objectives Study Guide 11.1 Introduction 11.2 Set-Reset Latch 11.3 Gated D Latch 11.4 Edge-Triggered D Flip-Flop 11.5 S-R Flip-Flop 11.6 J-K Flip-Flop 11.7 T Flip-Flop.. 11.8

Any changes to discovery configuration file, like most of the configuration files within OpenNMS, requires that OpenNMS be restarted.. Second, what if you want to discover a

Amiata (Southern Tuscany), an extinct volcano. The measured parameters are: T, pH, Eh, EC, dissolved CO 2 and CH 4. The results of three years of continuous monitoring can be

Antioxidant and dexamethasone treated groups (groups C and D) showed a significant decrease in 9 serum IL-4 levels as compared to induced bronchial asthma group (group B).. Journal

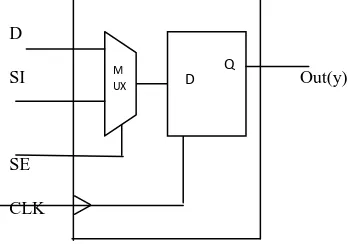

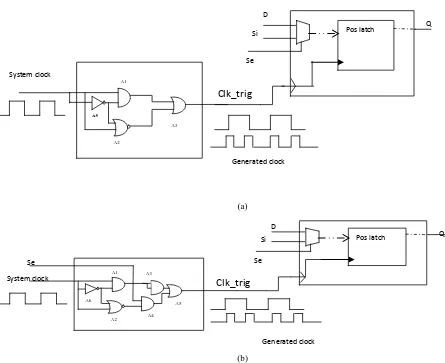

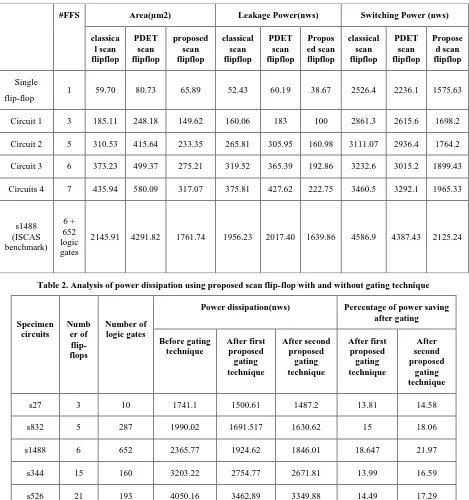

particularly, many hybrid BIST schemes store settled indefinite quantity patterns (used to sight random pattern resistant faults) on the tester in an