Power Efficient Radix-2 DIT FFT using Folding Technique and DKG Reversible Gate

Full text

Figure

Related documents

BKG half adder shows 84.17% reduction in the power consumption when compared to half adder implemented using Feynman and Fredkin reversible gate.. It also shows a 79.59% and

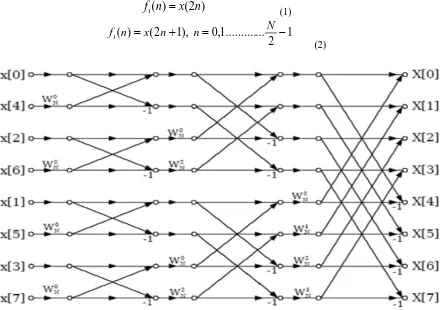

The Radix-8 Decimation-In-Time and Decimation-In-Frequency Fast Fourier Transform (FFTs) gain their speed by reusing the results of smaller, intermediate

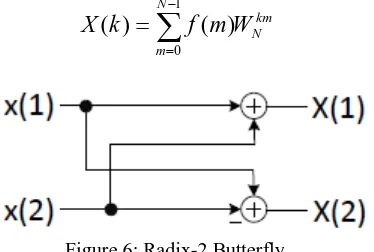

The fast Fourier transform (FFT) is one of the most important algorithms in the field of digital signal processing, used to calculate the discrete Fourier

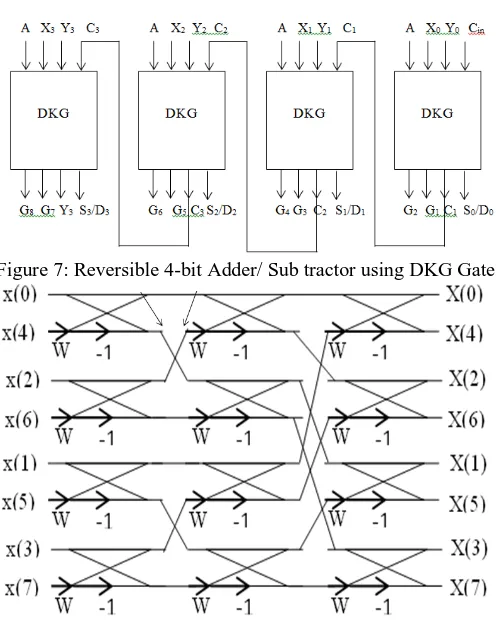

The proposed method revolves around the design of a Floating point adder architecture using reversible logic. gates such as Fredkin gate (FRG) , Feynman (FG) gates and Peres

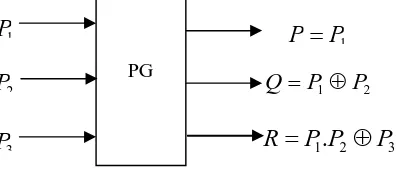

The below figure (1) shows the block diagram of fault tolerant reversible gates which is given by Fredkin and Feynman double gate (F2G) with their quantum

area efficient as well as high speed multipliers and adders in Fast Fourier Transform will ensure.. enhanced performance and

The paper proposes efficient MOS implementation for the basic reversible gates namely, Feynman, Toffoli, and Peres gates and employs the proposed circuits in the

After that we replace the reversible parallel adder by modified reversible adder then we compare both the multiplier and compare the terms like garbage outputs, power