Rigorous analog verification of asynchronous circuits

Full text

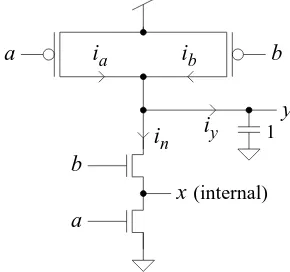

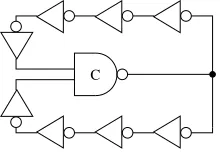

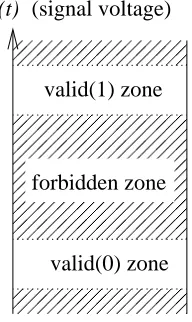

Figure

Related documents

The mechanism by which cardiovascular patients have a higher risk of contracting COVID-19 and developing more severe disease is unknown, but potentially may be due to

The overall goal of this study was to develop an interactive-computer system using cell phones for real-time collection and transmission of adverse events related to

Front-End Lexicon Acoustic Model Language Model Search Adaptation ASR: sonic. University of Colorado, Center for Spoken Language Research

In the article’s main, second and third parts, it is demonstrated how despite this multiplicity of voices the high-profile career of the amir Qurqum ā s appears coherently

For life satisfaction the first two WVS values for the total population are used, together with the Latinobarometer data starting 2000.. Where the WVS and Latinobarometer

A test of burn severity effects on the ratio of live (survived plus regrowth) to standing dead coniferous species and the interaction of burn severity in the ground layer (moss

Aim: Evaluation of serum levels of 17 cytokines and 5 adhesion molecules in patients with newly diagnosed acute myeloid leukemia.. (AML) using biochip

From the analysis of the data we can conclude that the lack of ongoing training and the lack of knowledge and experience required for accountants and auditors