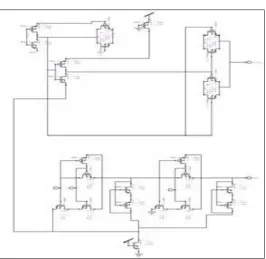

An Improved Low Power, High Speed CMOS Adder Design for Multiplier

Full text

Figure

Related documents

Therefore, the aim of this study was to evaluate mesio- distal tooth width of permanent teeth in patients with complete unilateral cleft lip and palate, by comparing tooth size

Interest- ingly, a single cell whole genome sequencing study for colon cancer identified an abundant amount of mutated gene SLC12A5 at the individual level, which was sparse at

Abstract: The paper presents the FEM method for determination of boiling heat transfer coefficient in cooling liquid flow in a rectangular minichannel with asymmetric

However, our results suggest that, in budding yeast, the func- tional contribution of H2A.Z to DSB formation, if any, is only minor: (1) dynamics of Hop1 phosphorylation at T318,

• Promoting a coherent, integrated approach, whereby the management of C&D waste is given due consideration throughout the life cycle and duration of a

The secondary information were through literature review on the subject matter, while the primary sources involved: first, a reconnaissance survey of the study

This is an open access article distributed under the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided

The main role of the service providers is to maintain privacy of the users where their confidential information is stored in the cloud. Due to insufficient user control,