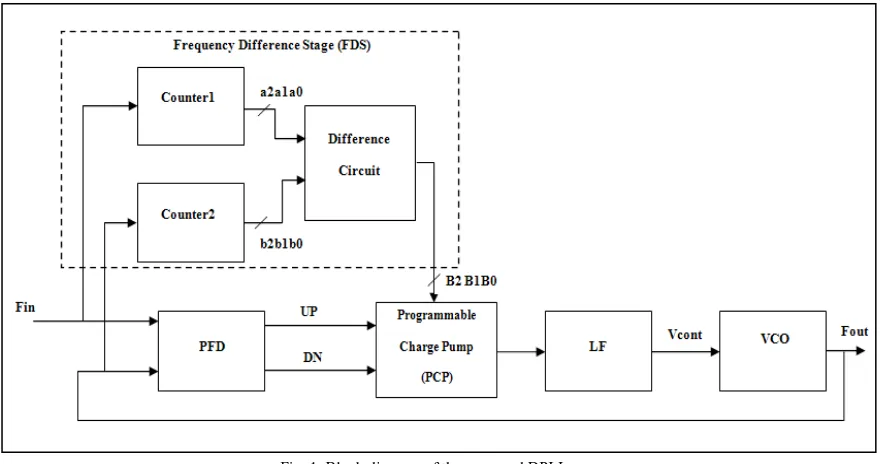

A Fast Locking Digital Phase-Locked Loop using Frequency Difference Stage

Full text

Figure

Related documents

We propose and examine a simple model for credit migration and spread curves of a single firm both under the real-world and the risk- neutral measure.. Default is triggered either

Figure 4: Continuous Ranked Probability Skill Score versus lead time for the TIGGE-4 multi-model (solid line), for the contributing single-models itself (dotted

Our results show that functional brain connectivity alterations can be identified before the development of full blown psychosis in 22q11DS and involve regions already known to

Based on the measurement of the performance system ca be concluded that the queuing system and service given are good and effective (seen from performance measurement and

We excluded bilateral knee arthroplasty, leaving 141 UKA and 245 TKA who rated their satisfaction and expectation regarding pain, range of motion (ROM), daily living function

A candidate having at least 2 nd division in FA/FSc is eligible for admission. Candidates having 3 rd division in FA/FSc are not eligible for admission in the

IFRS takes the value one if the firm has adopted IFRS and zero otherwise; SIZE is the natural logarithm of the year-end market value of equity; RET is the raw annual stock