Dual Mode Logic – Design For Energy Efficiency And High Performance Carry Skip Adder

Full text

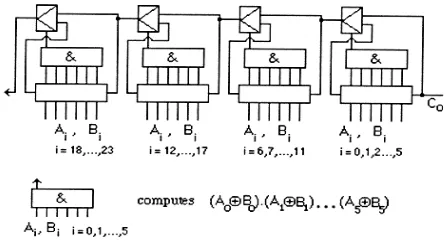

Figure

Related documents

Hence, using this photodiode efficiently with a very efficient and modified code, one must be able to obtain a data rate of 500 bits/sec upon connecting to Arduino..

: 29 French adult patients with PMM2- congenital disorder of glycosylation: outcome of the classical pediatric phenotype and depiction of a late-onset phenotype. Orphanet Journal

Chlorophyll destruction in older leaves and its biosynthesis inhibition in Figure 1 An overview of effects of Cd exposure to plants at different levels in photosynthetic machinery..

alternative methods for testing a single unit root in a general time series... k large and

Past cattle feeder research has shown that cattle feed conversion, average daily gains, mortality rates, and health are significantly affected by variables such as gender, location

The Intestinal Crypt,A Prototype Stem Cell Compartment.. Introduction to Probability

Di ff erential cross section measurements were reported with both the lepton + jets and the dilepton channels as a function of many observables of the recon- structed top candidates,

In figure 1(b) is visualized the functionality of a fuzzy neural network, in this case XBASE, with different activation functions. In an intelligent grid, it is