NIOS II Soft-Core Processor Based Wireless Notice Board

Full text

Figure

Related documents

In this implementation, the three components of an application (i.e., presentation, processing, and data) are divided among two software entities or tiers: client application code

An enhanced education APICS education is designed to help corporations enhance the knowledge and skills of their supply chain and operations management professionals..

Major trauma induces an inflammatory response initially characterized by increased levels of proinflammatory cytokines and activation of neutrophils.. This pathophysi-

■ Device drivers—For information, refer to “Nios II Embedded Software Projects” in the Nios II Software Build Tools chapter of the Nios II Software Developer’s Handbook..

f The Nios II Software Build Tools chapter of the Nios II Software Developer’s Handbook provides detailed information about creating makefiles.. For a description of Nios II

• Displacement mode – the effective address of the operand is the sum of the contents of a register and a signed 16-bit displacement value given in the instruction.. • Register

The Nios II architecture supports a JTAG debug module that provides on-chip emulation features to control the processor remotely from a host PC.. PC-based software debugging

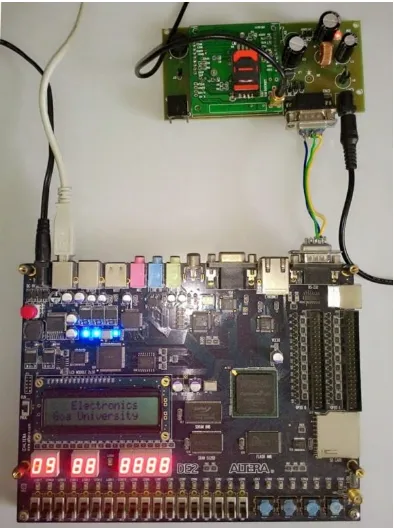

In our discussion of Figure 11 in Section 3.1, we showed how the Monitor Program can be used to download a prebuilt Nios II hardware system onto an FPGA board, when the Nios