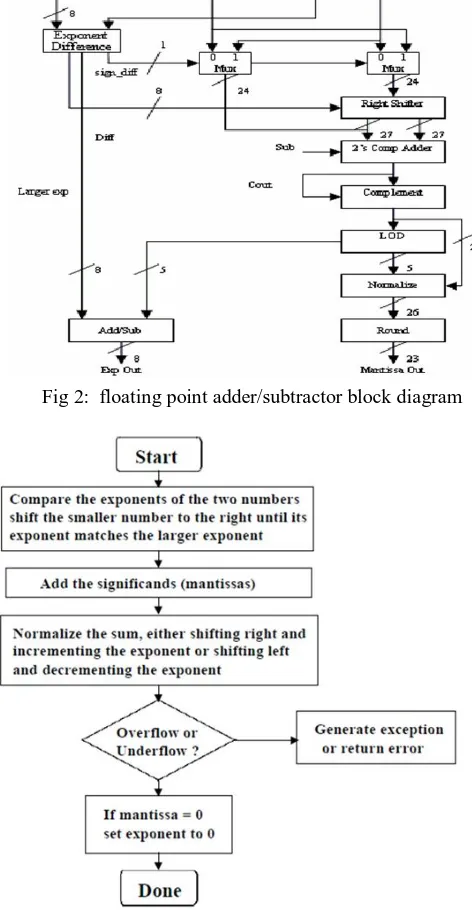

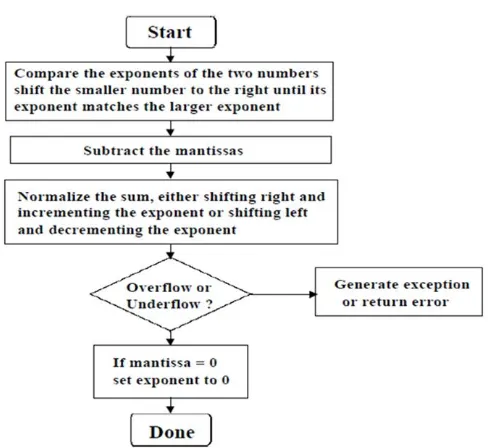

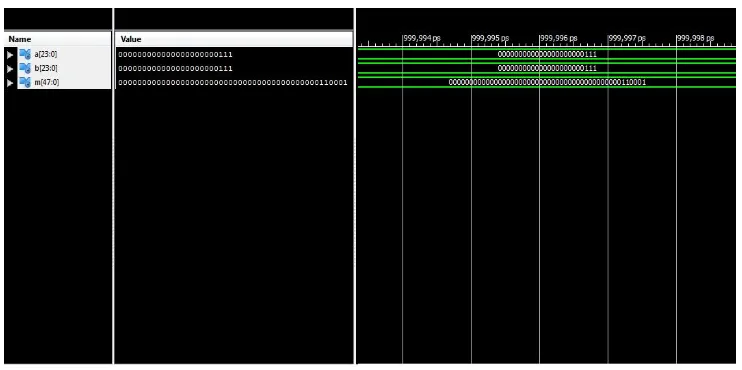

Design and Simulation of Floating Point Adder, Subtractor & 24 Bit Vedic Multiplier

Full text

Figure

Related documents

However when the cells were cultured invitro with SLP along with bacterial lysate (from corn oil induced SLP group), a significant decrease in the cytokines level was observed

InterviewBryant2596 4b pm Regeneration and pattern formation an interview with Susan Bryant MICHAEL K RICHARDSON*,1 and CHENG MING CHUONG2 1Institute of Biology, Leiden University,

The aim of this study was threefold: (i) to analyze samples of oral fluid and self-reported data from questionnaires to investigate the prevalence of alcohol and drugs among a sample

Thus, the length of detected tracts reflects the gene conversion initiation rate rather than the real tract length, and GENECONV has very limited power when gene conversion is

The Cdc68 N-terminal domain is altered by tempera- ture-sensitive point mutations: In cdc68-1 and cdc68-197 cells certain noncomplementing plasmids harboring only fragments of the

In this design we considered one of x-band motion detector module as a radar and the second x-band motion detector as jammer circuit which uses Doppler frequency principle

Most paternally repressed imprinted genes are indeed not associated with DMRs but are controlled in cis by paternally expressed nontranslated RNAs because very long