An efficient interpolation filter VLSI architecture for HEVC standard

Full text

Figure

![Table 4 Comparisons of our previous works [18] and proposednew algorithm compared to HEVC](https://thumb-us.123doks.com/thumbv2/123dok_us/890837.1107173/6.595.56.291.111.333/table-comparisons-previous-works-proposednew-algorithm-compared-hevc.webp)

Related documents

[r]

This paper manages a productive execution of Discrete Cosine Transform (DCT) pieces utilized in video pressure based on the High Efficiency Video Coding (HEVC) standard.. The

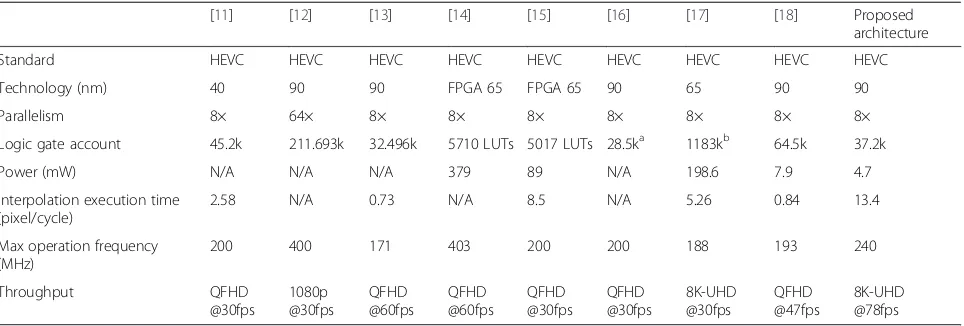

This paper Presents an efficient way of reducing the delay and area by two-step optimization technique for designing a reconfigurable VLSI architecture of an interpolation filter

(e,f) Caspase 3/7 activation analysis in rat neonatal cardiomyocytes (e) and HL-1 cells (f) transduced with AAV9-ghrelin or AAV9-control and treated with doxorubicin 0.5 mM and 1

Our findings indicate that no proximal X-chromosome deficiency is by itself able to cause male sterility; however, certain deficiencies in combination with duplications

The new policies are proposed in cloud where access legitimacy of user and updating cipher text security designated by data owner are two critical challenges to make

ability of these mutant proteins to repress str-2 expres- the E403Q mutant in the AWC neurons were similar to those of animals expressing the wild-type odr-7 cDNA sion was

We propose a general formal PoR model with public variability for cloud data storage, in which both block less and stateless verification are achieved simultaneously; The proposed