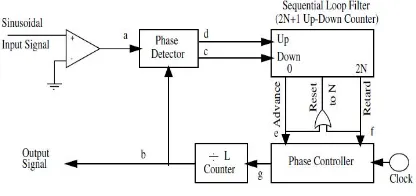

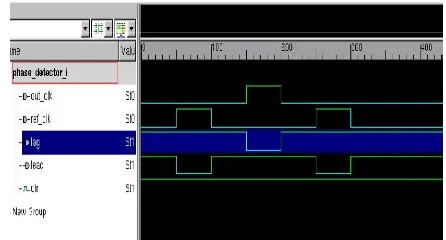

Implementation of Low Power All Digital Phase Locked Loop

Full text

Figure

Related documents

When a customer advises Xcel Energy’s Business Solutions Center prior to the disconnection of service that any part of the billing as rendered or any part of the service is

The study showed increased risks consistently in the exposure group where the risks were most likely to be detected first: in the highest exposure group, the persons that had used

a) receiving video information from two hockey goals using color video cameras for a full view of the goal area with cameras in the goal net, behind the goal net and above the

D MDA-MB- 468 cells that were either untransfected or expressing GFP, GFP-Bax, GFP-Bax S184A, or GFP-Bax S184E were treated with ABT-737 (100 nM, 48 h), and apoptosis was evaluated

Cilj ovog istraživanja bio je utvrditi utjecaj gnojidbe na hibride sirka primjenom različitih gnojiva, utvrditi koji hibridi su postigli najvišu masu pri berbi, a koji

[r]

IBM Service provides hardware problem determination on non-IBM parts (adapter cards, PCMCIA cards, disk drives, memory, and so forth) installed within IBM systems covered under

At the 2012 ABA annual meeting, the House of DelegateS71 approved Recommendation 501A sponsored by the ABA Commission on Ethics 20/20 amending the Model Rules