Title: IMPLEMENTATION OF LOW POWER LOW NOISE PROBABILISTIC-BASED LOGIC DESIGNS

Full text

Figure

Related documents

78. Pulse –Echo Shear Wave Ultrasonics 79. A shim shall be fabricated of radiographically similar material to the object to be inspected... a) An examination of a welded

In case of operation with push-pull type weeders, push force is utilized for weeding whereas pull force is required for repositioning the equipment to generate acceleration in

This is an open access article distributed under the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided

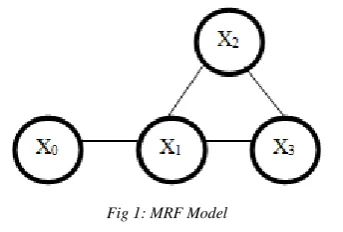

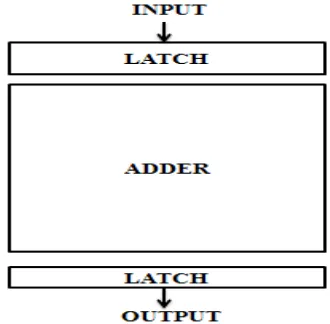

The projected style on comparison with the normal full adder composed of CMOS transistors, transmission gates and Complementary Pass-Transistor Logic (CPL),

Three input and the five input majority function have been used in the proposed adder. The full adder operation can be stated as follows: given the three inputs A, B and C. it

Static CMOS logic provides several advantages in designing digital circuit, that are low sensitivity to noise, good performance, low power consumption, etc.. But

Violent acts of sexual exploitation or rape are. usually perpetrated by males under the age

The ensemble sensitivity analysis results are consistent with the formation of this stationary convective rainband being caused by flow separation upstream of the Lake