Multi Bit Errors Prediction and Correction in Memories Using Cost Efficient 64 Bit DMC

Full text

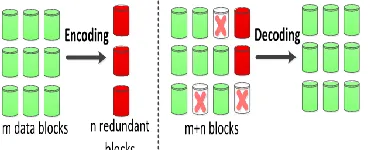

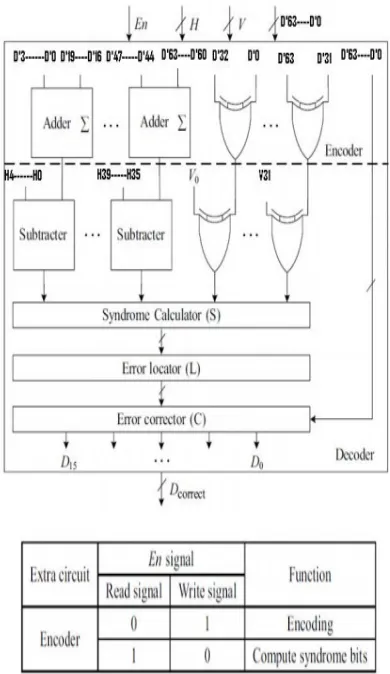

Figure

Related documents

Linezolid was administered into five car- tridges as a 1-h infusion via computer-controlled syringe pumps to sim- ulate the free (non-protein-bound)-drug 24-h area under

Post-operative complications were highest in diabetic patients, requiring proximal re-amputation, secondary, suturing, skin grafting and stump refashioning, Below knee amputations,

O -glycan metabolism with high expression of sentinel susC -like genes from the homogalacturonan, levan, and chondroitin sulfate PULs early and reciprocal patterns for nearly all of

We are proposing that the immunological defect of these siblings fits a pattern of a familial variable immunodeficiency (common variable immunodeficiency with predominant

w Cle-cured bed- bugs reared on rabbit blood supplemented with riboflavin and biotin exhibited similar levels of survival, adult emergence rate, FIG 2 Genomic regions

The most significant result of this study was the fact that if the two parameters (IgA/VCA test and C.T. scan) were used in combination (in series) in all suspected cases ofNPC not

The purpose of this hospital-based study is to establish the spectrum of rheumatic diseases seen on an outpatient basis over a 24-month period at the Rheumatology Clinic,

An anthropometric study and dietary investiga- tions were conducted in an Iban community in the Sixth Division of Sarawak. 140 children aged 0 to 6 years, were