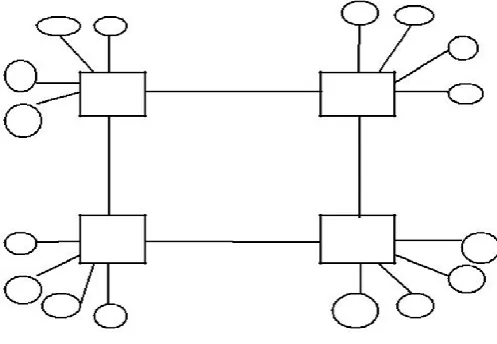

Design of low power network on chip using data encoding techniques

Full text

Figure

Related documents

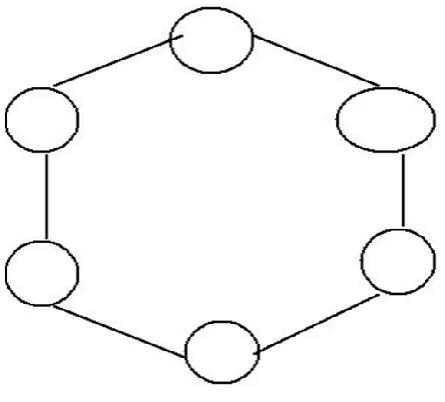

Introduction to Zigbee Technology Page 13 As shown in figure 5 above, the star topology has a central node with all other nodes communicating only with the central one.. The

In order to inform a wide range of audience of the ALLVET project and enhance its visibility, different dissemination materials will be prepared.. Dissemination materials will

Looking first at results of bivariate regression, parent’s income, work status, block group median income, road density, distance to nearest park and parents’ perceptions of social

Statistical Process Control (SPC), components of variance, Taguchi Loss Function, and reliability block diagrams (RBD) are used in this thesis for the evaluation of the supply

Definition: The National Plan and Strategy for Primary Education Teacher Education and Development (TED Plan; June 2011) defines the professional

Module 3: Connecting Providers and Managing High-Risk Beneficiaries; Module 2: Reshaping Care Delivery 3: Effective use of health information technology and data

The specific need to assess the strength of in-situ concrete has led to the development of a range of tests in which the surface zone is penetrated or

In addition, CBC is required by law to provide clients with notice of its legal duties and privacy practices with respect to protected health information. That is the purpose of