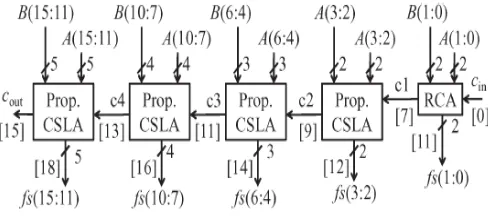

Area–Delay–Power Efficient Carry-Select Adder

Full text

Figure

Related documents

evidences that young breast cancer patients have worse prognosis compared with older ones. Since young breast cancer patients have more aggressive clinicopathological

The aim of this paper is to give an overview of the development process of a computer-based job task analysis instrument for real-time observations to quantify the job tasks

Since it is difficult to estimate the num- ber and positions of fish in a cluster, in the proposed method, we begin to track only isolated fish that do not overlap with

Rainfall data being more available, a rainfall-runoff model was developed on Mefou Nkol-Bisson watershed using artificial neural networks to allow the prediction of runoff from

Due to the nature of chitosan, none of the selected methods were able to successfully remove free IL-12 and maintain detection of the chitosan-IL-12 conjugate.. Future strategies for

There- fore, the majority of sequence differences observed within the collected family members define the se- quence of actively propagating LINE-1

This study aimed to determine the prevalence of chronic suppurative otitis media as seen in the University of Port Harcourt Teaching Hospital (UPTH), Port Harcourt with a

While multi-hop broadcast protocols, such as Trickle, Deluge and MNP, have gained tremendous popularity as a means for fast and convenient propagation of data/code in