Ultra-Low Power Design of Digital CMOS Logic Circuits

Full text

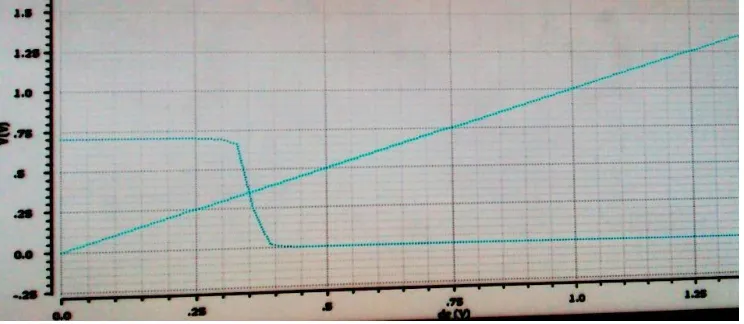

Figure

Related documents

We are comparing the different parameters like packets received ratio, packet dropped, delivery rate, Average end to end delay and average throughput for different number of nodes

The sub-categories of risks in internal operations of logistics service providers are process design and planning risks, quality risks, lead time risks, breakdown and hazard risks, IT

thesis[ 1 ℄ used Frank Pfenning's[ 30 ℄ lemma insertion (user dependent) proof transformation in order to extrat tail reursive programs from proofs. Finally Chiarabini [ 9 ℄

fgUnh fo”o dks’k ds vuqlkj psruk** tho/kkfj;ksa esa jgus okyk og rRo gS tks mUgsa futhZo inkFkksZa ls fHkUu cukrk gSA nwljs “kCnksa esa ge mls euq’; dks thou

The most promising biomarker to date is the epidermal growth factor receptor (EGFR) mutation status; recent data suggest that compared to patients with tumors lacking such

Therefore, extending the probe scaffold by appending an ubiquitin or target protein peptide onto the C-terminus of a Ubiquitin probe beyond the electrophilic trap can

Having cows at a desirable body weight and body condition scores through the grazing of corn crop residues and stockpiled forages will reduce the amount of stored forage required

We can show that the total energy (kinetic plus potential energy) of a conserved system is a constant of motion or invariant in time for a one dimensional system.