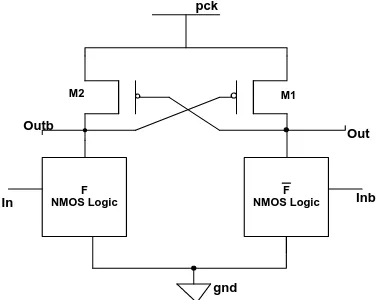

Ultra Low Power Dissipation in Adiabatic Logic Circuits in DSM Technology

Full text

Figure

Related documents

PFGE, Lior serotype, and antimicrobial resistance patterns among Campylobacter jejuni isolated from travelers and US military personnel with acute diarrhea in Thailand, 1998 –

WHO: World Health Organisation; TAG: Topic Advisory Group; ICD: International Classification of Diseases; ICD-11: 11th version of ICD; iCAT: Collaborative authoring tool for ICD11;

Below, the real-time dynamics in consequence of local quenches will be studied for an interaction quench in the Kondo model (Sec. 2.1), for the sudden switch on of a mobile impurity

15 EPEC posi- tive samples from children below one year of age were detected by routine screening and of the positive results for EPEC or EAEC in the group of samples from chil-

The sub-categories of risks in internal operations of logistics service providers are process design and planning risks, quality risks, lead time risks, breakdown and hazard risks, IT

In fact, when excited by high-frequency signal, the phase relevant to the three right-hand circularly polarized (RHCP) wave components radiated from the currents on the three

A multivariate analysis revealed varied predictors of depression: nationality, family history of depression, negative life events, job dissatisfaction, a long working week, little

The paper presented the performance evaluation of different distance measures used in color iris authentication.. The iris features are extracted