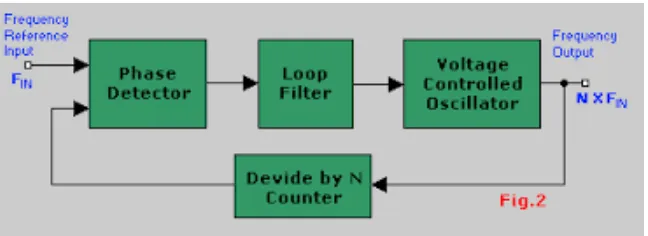

Design of a Low-Power Low-Noise Phase Lock Loop

Full text

Figure

Related documents

For a given eccentricity, the occurrence of juvenile wood combined with the viscoelasticity of wood allows the tree to use higher pre-stresses in reaction wood and consequently

Measures included reach (patient participation rates, characteristics, and receipt of services), adoption (nurse participation rates and characteristics), implementation

Linear programming is the common method of Least Cost Feed Formulation which compares the nutrients required by the animal to the nutrients supplied by the

We can make the system easier to use by implementing it using a single microcontroller connected with a small module mounted near the larger solar panelsand then sending

To improve the performance of the AC motor speed control system and understand the vector control technology in depth, the studying of the asynchronous motor mathematical model and

Although clinical cross-reactivity between nuts may be dif- ficult to establish, the possibility of exhibiting symptoms of food allergy to multiple nuts plays an important

The capability of the proposed constitutive model to predict the deformation behaviour of orthotropic materials under high pressure and shockwave including spall failure

The frequency of crossing over between the sites of mutations concerned with different enzymatic steps can be estimated on the basis of the average (and quite constant) yield