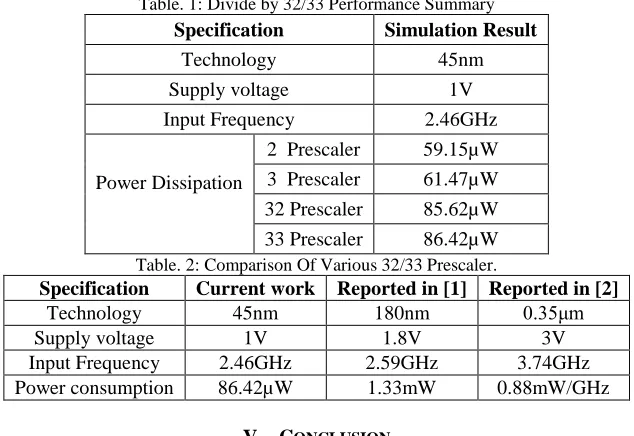

CMOS Low Power, High Speed Dual-Modulus 32/33 Prescaler in sub-nanometer Technology

Full text

Figure

Related documents

Much like the electrical power that is received each day, cloud computing provides subscribers or users with access to a shared collection of computing

The main objectives for demonetization was to restrain corruption, to curb the use of high denomination notes for terrorist activities, destroy fake currency and making black money

Finally, the paper attributes liberal policies measures in developing countries to the presence of a strong positive association between the “official development

(1) and (2) are the average size distributions during and after school hours in both the preschool centre and classroom for the whole sampling period;. (3) and (4) are the average

Reflections on aesthetic

Given the increased blood loss, operative time and fiscal cost associated with long com- pared to short CMN, regardless of whether refracture or reoperation rates are

Against this background, resource flows for financing development are a critical challenge for the continent: 28 of the 38 severely indebted low-income countries in 1998 are located

To further investigate potential reasons for the observed differences in the frequency of methylation between the high- and low/intermediate-grade tumour cohorts for specific genes,