Design and Implementation of FFT Processor Using Vedic Multiplier With High Throughput

Full text

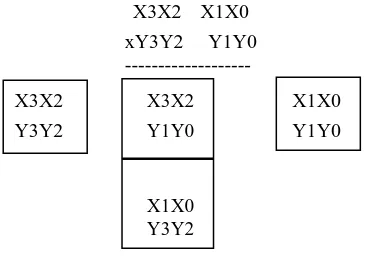

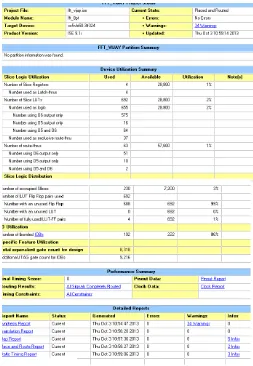

Figure

Related documents

Click or hit key on keyboard to move a short payment from Medical aid column to Patient due column within the selected line / billed item.. Click, ‘Accept Changes’

Without consideration of their age, numbers of lamina propria Foxp3-positive lymphocytes were significantly increased in the villus compared to the basal crypt area as well as

We make use of previ- ously collected data on social encounters specifically designed to measure heterogeneity in numbers of contacts amongst the British population, and fit

This, however, is an appearance only; the first metaphase shows ten chromosomes and is followed by a normal cell division and formation of two equal second

The vertical response of pile group calculated using the Elastic Layers model is shown as a solid line and compared with the measured data in Figure 4.. As seen in Figure 4,

Therefore, multi-pronged strategy should be adopted for ensuring the food security to all in general and weaker section in particular through proper implementation of anti-poverty

Oral processing parameters that characterize the properties of an average chewing cycle within the sequence such as average muscle activities or cycle peak activities, durations

Thus, in this paper the researchers proposed narrative analysis as a useful method for gathering valid evidences and digging long missing data, which can be