Rochester Institute of Technology

RIT Scholar Works

Theses

Thesis/Dissertation Collections

6-17-1996

Boundary scan system design

Craig Loomis

Follow this and additional works at:

http://scholarworks.rit.edu/theses

This Thesis is brought to you for free and open access by the Thesis/Dissertation Collections at RIT Scholar Works. It has been accepted for inclusion in Theses by an authorized administrator of RIT Scholar Works. For more information, please contactritscholarworks@rit.edu.

Recommended Citation

Approved By:

BOUNDARY SCAN SYSTEM DESIGN

by

Craig R. Loomis

A Thesis Submitted

In

Partial Fulfillment

of the

Requirements for the Degree of

MASTER OF SCIENCE in Computer Engineering

George A. Brown, Professor and Thesis Advisor

Dr. Pratapa V. Reddy, Associate Professor

Dr. Robert E. Pearson, Associate Professor

Dr. Roy Czemikowski, Department Head

DEPARTMENT OF COMPUTER ENGINEERING

COLLEGE OF ENGINEERING

ROCHESTER INSTITUTE OF TECHNOLOGY

ROCHESTER, NEW YORK

THESIS RELEASE PERMISSION FORM

COLLEGE OF ENGINEERING

ROCHESTER INSTITUTE OF TECHNOLOGY

Title of Thesis: Boundary Scan System Design

I, Craig

R.

Loomis, hereby grant pennission to the Wallace Memorial Library of

Rochester Institute of Technology to reproduce this thesis in whole or in part. Any

reproduction will not be for commercial use or profit.

ABSTRACT

Given the strong competition in digital designon the national and international

levels,

boundary

scan devices arerapidlybecoming

a necessary as opposed to aconvenientfeature on integrated circuits. This thesis serves adualpurpose.

First,

it demonstrateshow

boundary

scan devices canbe used toincrease the testabilityof acircuit and itpresents several factors used toquantify the cost associated with the addition of

boundary

scan compatibility todigital designs. Costtradeoffs are often the most

intimidating

hurdle forengineers to cross when

deciding

ifboundary

scancompatibility is worth theeffort.

Second,

itdemonstrates theuse oftheTektronix LV500 (logic verifier) as ageneral testing tool, using

boundary

scan designs as examples. These examples providean understandingofthe function of

boundary

scancells and theJTAG/1 149. 1 standard.The LV500, which is used

by

studentsin the DepartmentofComputerEngineering

andMicroelectronic

Engineering

atRIT,

is anindispensable tool for makingcriticaltimingmeasurements. It also allows a userto evaluate and step through simple as well as more

complicateddesigns. It is my hope that this thesis and the tutorialprovided will facilitate

the use ofthe LV500 in future testingworkperformed in RIT'scenterfor

Microelectronic and Computer

Engineering

clean roomfacilities. Uponfollowing

theexample circuits

described,

one shouldbecome familiarwithboundary

scan terminologyTableofContents

List ofFigures vii

ListofTables ix

Glossary

x1.0 Introduction and

History

11.1

Testability History

11.1.1 ImportantCharacteristics of

Testability

21.1.2 Current

Testability

Issues 41.2 How

Testability

HasBeenImplemented 81.2.1 Fault Types 9

1.2.2 TwoRequirementsofFault Detection 10

1.2.3 A ClassicalExample 1 1

1.3 LimitsofClassic Example 12

1.3.1

Increasing Density

ofICs 121.3.2

Increasing Density

ofPCBs 131.3.3 Physical Interface withBed-of-Nails 14

1.4

Boundary

Scan Alternative 151.4.1 The Basics 16

1.4.2

Overcoming

Density

ofICs 191.4.3

Overcoming Density

ofPCBs andPhysical Interface 191.5 ProblemStatement 20

1.6 SystemConstraints 21

1.7

Terminology

221.7.1 JTAG Specifications 22

1.7.2 TektronixLV500 27

2.0 Functional Specifications 28

2.1 Overview ofTutorial 28

2.2 LV500

Setup

and Configuration 292.2.1 Menus 29

2.2.2 Testhead Installation 33

2.3 40 pin ZIF Testhead 34

3.0 Tutorial for Test Boards 36

3.1 SingleTest

Chip

363.1.1 BSCANJTest

Setup

363.1.1.1 DUT

Wiring

393.1.1.2 LV500

Setup

423.1.1.3 Pattern Test Vectors 50

3.1.2 Single

Stepping

Test 543.1.3 Schmoo Specification 65

3.1.3.1 InputVoltage Limits 66

3.1.3.2 Propagation

Delay

693.2 Single

Chip

with Combinational Logic 733.2.2 Design ofState Machine 73

3.2.3 BSCANJITest

Setup

843.2.3.1 DUT

Wiring

853.2.3.2 LV500

Setup

883.2.3.3 Pattern Test Vectors 89

3.2.4

Running

Test 903.2.5 Schmoo Specification Tests 99

3.2.5.1 TCKPulse Parameters 99

3.3

Boundary

Scan Circuit Design 1053.3.1 LogicDesign atthe IClevel 105

3.3.2

Boundary

Scan Architecture Features 1063.3.3 The Design Overview 107

3.3.4 The DesignDetails 119

3.3.4.1 DesignoftheTAP 119

3.3.4.2 Designofthe Instruction Register 125

3.3.4.3 Design ofthe BypassRegister 129

3.3.4.4 Designofthe

Boundary

Scan Register 1303.3.4.5 Design ofthe Custom Scan Register 133

3.3.5

Summary

ofBoundary

Scan CircuitDesign 1354.0

Summary

And Conclusion 1384.1 DesignDetails 138

4.2 Problems Encountered and

Remaining

Limitations 1414.3 Suggestions forFuture Enhancements 141

5.0 References 142

APPENDIX A

Listing

ofTiming

Diagrams 145APPENDIX B Code Generation 154

B.l Unix Applications 154

B.l.l

Peg

InputCommands 154B.1.2

Peg

Eqn Output (Eqntott InputFile)

155B.1.3

Peg

Summary

Output File 156B.1.4

Peg

Truth-Table Output File 156B.l. 5 Eqntott Output File (Espresso Input

File)

157B.1.6 Espresso Output File 158

B.2 MentorGraphics Simulation Files 159

B.2.1 QuickSim Input Files 159

B.2.2 QuickFault Input Files 165

B.2.3 QuickFault Output File 171

B.3 LV500 Input File 174

B.3.1 BSCAN I.NEWPattern File 175

B.3.2 BSCAN II.NEW Pattern File 178

APPENDIX C Discussion of

Printing

Operation 180APPENDIXD Contacts 181

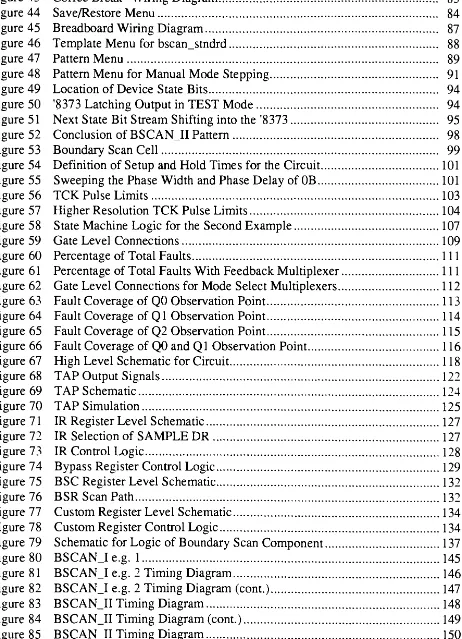

Table ofFigures

Figure 1 Average NumberofFaults

During

Product Life Cycle 5 Figure 2 Relative CostofRepairing

aProductDuring

Life Cycle 6 Figure 3 TotalTime Requiredto Generate Test Patterns 8Figure 4 Circuit ExampleofLogical Faults 9

Figure 5 Recent Trends in Gate-to-Pin Ratio 13

Figure 6

Boundary

Scan Cell 17Figure 7

Boundary

Scan Path on PCB 18Figure 8

Boundary

Scan Architecture 24Figure 9 TAP State Diagram 25

Figure 10 LV500 Keyboard 30

Figure 11 Power

Up

Menu 32Figure 12 Main Selection Menu 32

Figure 13 LV500 SystemConfiguration 34

Figure 14 40pin ZIF

Wiring

Diagram 35Figure 15 Save/Restore Menu 37

Figure 16 Testhead

Wiring

Diagram 38Figure 17 DUT

Wiring

Menu 41Figure 18 Channel D Menu 44

Figure 19 Channel

Q

Menu 44Figure 20 Detail ofClock Phase Signals 45

Figure 21 Template Menu bscan_stndrd 46

Figure 22 Template Menu play_templat 47

Figure 23 Pattern Menu 50

Figure 24 POWERJJP Macro Menu 51

Figure 25 RESET Macro Menu 51

Figure 26

Config

Menu 53Figure 27 BYPASS Scan Register 56

Figure 28 Instruction Register 57

Figure 29 Placement ofSingle

Step

Commands 60Figure 30 SAMPLE Scan Register 62

Figure 31

Setting

Bit D8 High toFlag

Error 64Figure 32

Replacing

mask_TDI with mask_LATCH template 64Figure 33 Define Schmoo Menu 65

Figure 34 Input VoltageLimits 68

Figure 35

Determining

propagation time from D toQ

70Figure 36 Propagation

Delay

Time 72Figure 37 Coffee Break 75

Figure 38 Gate Level Connections 79

Figure 39 Percentage ofTotal Faults 80

Figure 40 Faults perCycle 80

Figure 41 Control andTestLatches 82

Figure 42 Detail Switch Schematic 82

Figure 43 Coffee

Break-Wiring

Diagram 83Figure 44 Save/Restore Menu 84

Figure 45 Breadboard

Wiring

Diagram 87Figure 46 Template Menu for bscan_stndrd 88

Figure 47 Pattern Menu 89

Figure 48 Pattern Menu for Manual Mode

Stepping

91Figure 49 Location ofDevice State Bits 94

Figure 50 '8373

Latching

Output in TEST Mode 94Figure 51 Next State Bit Stream

Shifting

intothe '8373 95Figure 52 ConclusionofBSCANJI Pattern 98

Figure 53

Boundary

Scan Cell 99Figure 54 Definition of

Setup

and Hold Times forthe Circuit 101Figure 55

Sweeping

the PhaseWidth and PhaseDelay

ofOB 101Figure 56 TCKPulseLimits 103

Figure 57 Higher Resolution TCKPulse Limits 104

Figure 58 State Machine Logic for the Second Example 107

Figure 59 Gate Level Connections 109

Figure 60 PercentageofTotalFaults Ill

Figure 61 Percentage ofTotalFaultsWith Feedback Multiplexer 1 1 1

Figure 62 Gate Level Connections for Mode Select Multiplexers 1 12

Figure 63 Fault CoverageofQ0 Observation Point 113

Figure 64 FaultCoverageofQl ObservationPoint 114

Figure 65 FaultCoverageofQ2 Observation Point 115

Figure 66 Fault Coverage ofQ0and Ql Observation Point 116

Figure 67 High Level Schematic forCircuit 118

Figure 68 TAPOutput Signals 122

Figure 69 TAP Schematic 124

Figure 70 TAP Simulation 125

Figure 71 IR Register Level Schematic 127

Figure 72 IR SelectionofSAMPLEDR 127

Figure 73 IRControl Logic 128

Figure 74 BypassRegisterControl Logic 129

Figure 75 BSC Register Level Schematic 132

Figure 76 BSR Scan Path 132

Figure 77 Custom Register Level Schematic 134

Figure 78 Custom RegisterControl Logic 134

Figure 79 Schematic for Logic of

Boundary

Scan Component 137Figure 80

BSCANJ

e.g. 1 145Figure 81

BSCANJ

e.g. 2Timing

Diagram 146Figure 82 BSCAN_I e.g. 2

Timing

Diagram(cont.)

147Figure 83 BSCANJI

Timing

Diagram 148Figure 84 BSCANJI

Timing

Diagram(cont.)

149Table ofTables

Table 1 Logical

Mapping

ofDUT 40Table 2 Description ofPhase Times for Figure 21 46

Table 3 Description ofPhase Times for Figure 22 47

Table 4 State Assignment Table 74

Table 5 State Transition Table 76

Table 6 DUT

Wiring

Table 86Table 7 TAP Output Signals 121

Table 8

Mapping

ofIR to its Address Instruction 126Table 9 NumberofLogic Cells Required forImplementation 139

Table 10

BSCANJ

Timing

Table e.g. 1 151Table 1 1

BSCANJ

Timing

Table e.g. 2 152Table 12 BSCANJI

Timing

Table 153Glossary

ASIC Application Specific Integrated Circuit. A type ofIC device that performs

specific pre-programmed functions suchascontrollingelectronicinstrument

panels andthe sensing offluid levels.

BIST Build In Self Test. Logic included in a design thatperforms a self-contained

self-testofthe device.

BSR

Boundary

Scan Register. A set of storage cellsthat use multiplexerstocontrolthe flow ofdatainto and out of an I/O pin. The I/Ocan bedirected from the

normal path to a serial shift register of similarBSRs.

DFT Design For Testability. A design methodology that channelsearly design efforts

toensurethat afinal design product is testable.

DIP Dual In-line Package. A rectangular plastic

housing

for ICand othercomponentsthat isused on PCBs.

DUT Device Under Test. Circuit that is

being

tested forfaults.IC Integrated Circuit, also called a

"chip."

An integrated arrayofactive and passive

elements with a single semiconductor substrate.

LFSR Linear Feedback Shift Register. A shiftregister with some ofitsoutputs

exclusively ORED togethertoforma feedbackmechanismwhich creates a

Pseudo-Random PatternGenerator.

LSSD Level Sensitive Scan Design. A design methodology thatensuresrace-free

operation. Itis based upon memoryelements thatare independent of signal

MCM

Multi-Chip

Module. A circuitformedby

placing ICson top of each other toincrease circuit

density

and decreasesignal tracelength.PCB PrintedCircuitBoard. The"platform"forelectronic circuit constructionthat

contains all theconnectionsbetween thecomponentsprinted on theboard.

PRPG Pseudo-Random Pattern Generator. ALFSR configured to generatedatatodrive

a logic block. It isoften used in conjunction withaPSA

during

testing.PSA Parallel Signature Analyzer. A LFSRused to compress the outputsofa logic

blockintoa testregister such thata unique value isobtained aftera testisrun.

SLSI Super Large Scale IC. An IC with 50,000 to 100,000transistors.

SMT Surface Mount Technology. A methodofmanufacturingPCBs in which chips

are fixed

directly

ontothe surface oftheboard instead ofbeing

solderedinto pre drilled holes.ULSI Ultra Large ScaleIC. An ICwith over 100,000 transistors.

VLSI

Very

Large Scale IC. An IC with5,000 to 50,000transistors. Itis also used withreference to an IC design with any large number oftransistors.

1.0

Introduction

andHistory

Boundary

scandevices can be usedtointernally

test theintegrity

of an IC (Integrated Circuit)1or MCM

(Multi-Chip

Module)2 thatisembedded in a system'sdesign.They

can also be used to testthe externalconnections betweencomponents3

that are onthe

same PCB (Printed Circuit

Board)

even ifsome ofthe components are notboundary

scannable themselves. Thekey

behindtheirutility is twofold.First,

isthe novel idea ofusing an IC built with serially connectedI/O (Inputand

Output)

pins that allowtest access.Second,

is the use of anIEEE standardto ensurecompatibility among different vendors. TheIEEE 1 149.1 Standard Test Access Port andBoundary-Scan Architecturedocument has been underdevelopment since themid 1980'swith its formal acceptance in

1990.4 This

thesis provides a brief

history

oftestability and recenttrends in technologythat haveresulted in the new

boundary

scan standard. Italsodiscusses how students inthe Computer

Engineering

and MicroelectronicEngineering

Departmentsat RITcan benefitby designing

circuits and ICs thatincorporate theboundary

scan standard.1.1

Testability

History

It has been said thattestability has been around eversince the cave man whoinvented the

club, knocked himselfoutwhile trying toprove itworked.5 This first

section gives a definition oftestability followed

by

recenthistory

showingwhyboundary

scan devices1.1.1

Important Characteristics

ofTestability

A circuit's testability is

becoming

a criticalrather than convenient feature for non-trivialdigital systemsdesigned today. Before

discussing

currenttrends in testability, it is first important to understand whattestability is. Onedefinition states,"Testability

is acharacteristic ofadesign which allowsthe status (operableor

inoperable)

ofa system orany ofits subsystemsto be confidently determinedin atimely fashion."6 The definition is good as it contains twooftheprimary ideasoftestability; namely the timeittakes to

perform a testandtheinformationthat the test provides.

Examining

these two ideas willprovide insight to the core ofmany testability issues. Let's start with the time ittakes to

performa test. Thistime is dependentupon the size ofthe design and the tools available

at the

facility

in whichthe tests are performed. In otherwords, it dependsupon how easyit is to exercise adesign toobtain a system of measured responses which ascertain

whetheritis

behaving

properly.7Thus,

by increasing

the access totestfeatures,

testability is increased. This is dependentupon the level andcomplexity ofthe system

being

tested. The systemlevel will vary fromtestingofVLSI(Very

Large ScaleIntegrated)

circuit wafers to testing a PCB (Printed Circuit Board). Thesystemcomplexity will vary in numbersofcomponentsor gates andin the degreeofdata abstraction. Forexample, tests

being

performed may varyfrom measuring a singlevoltage with a probingstation to measuring a matrix ofdigital voltageswith a logic

verifier.

The second aspect oftestability, the information that the tests provide, is driven

by

boththe level ofthedesign and thediagnostic detail requiredfor its evaluation. Asthe design

level varies from IC design to PCB

design,

the amountofinformation available changesinformation also increases withthe design level. Anotherreason is that the systems

complexity increases from monitoring voltage levelstomonitoring digitalabstractions

representing system states and controldata. There is muchresponsibility given to the

designerto make use ofthatinformation asbest they seefit. Attimes, it is sufficient to

acknowledge whetheratest haspassed ornot; whilein other instances a systemmay

have toprovide detailed diagnostic feedbackon its actionsin ordertoisolate possible

future faults. Forexample, in order todetectand correctearly design errorsthe cause of

the errormust first be found through testing.

Hence,

testing is not only performed todetectfaults but also to determine the cause of aknownfault or misbehaviorin the

system.

Again,

depending

upon the levelofdesign,

this may targetanything from thedetection of a misaligned maskthat causes a shortbetween twopolysilicon lines on a

VLSI wafer, totheclock signal that hasan intermittent errorin a PCB. The important

thingto rememberisthat the value ofacircuit's testabilitylies notonly in how easy it is

1.1.2

Current

Testability

Issues

Now that the characteristics thatmake up

testability

havebeendiscussed,

let's focus onbusinessconcerns andthepotential impact thata design's testability hason its life cycle.

Threeofthe mainissues in adesign are thereliability, costand time to market. The

reliability ofadesign relates to howit functions both aftermanufacturing andwhen it is

being

usedby

a customer. The design should operate as specifiedforthe longesttimepossible. For some

designs, (e.g.,

medical equipment) reliability, relatingtothe safetyand well

being

ofitsusers, is themost critical issue. In otherdesigns,

thedesire tominimize failures and maximize product reputationdrivesthe increasesofproduct

reliability. Cost is anotherissue from acustomer's standpoint. It should stay within initial budget constraintsforthe lifeofthe product, notjustwhile

being

manufactured.The final issue is the time tomarket fortheproduct.

Having

a product available when acustomer needs ordesires

it,

is often referred to as themarket window. The firstcompany to ship products

during

this time will maintain ahigh market share.Again,

thishelps to determine the overall cost oftheproduct. These threeissues areverymuch

related with each

being

intimately

linked to testability.Reliability

may show the strongest link totestability since it increases proportional toincreased testing.

Simply

stated, the more aspects ofa system tested, the fewerpotentialfaults reach thecustomer. Onelink between design reliabilityandincreased testability

relates to component

failure,

as shown in Figure 1. The averagereliability of a product is boundedby

two stages ofincreasedcomponent failure. The second stage, shown on theright halfofthe Figure 1, represents"old

age."

This canbe theresultof metal migration,

can occur. Forthisreasonit is especially importanttorun adesign through itstest stages

during

a "burn in"periodpriortocustomer release.InfantMortality

OldAge

TypicalCurve

AgeofDesign

Figure 1 AverageNumberofFaults

During

ProductLife Cycle. Fora typicalproduct, the averagenumberoffaultsis bounded

by

infantmoralityand old age.

As forthe relationship between overallproduct costand testability, the cost typically

decreases withincreasedproducttestability. Inparticular,the costof

fixing

afaulty

product is much lowerwhen thefault iscaught early in the product life cycle. Figure 2

provides a graph

describing

the"Rule of 10's"where thecostof

detecting

andrepairing afaultincreases tenfold at each progressing stage oftheproduct's lifecycle. As an

example, assumethata misaligned mask has causeda trace tocreatea short circuit

between twooutput signals. In

discovering

this circuitflaw before packaging the wafer,the cost would encompass theprocessing and replacement ofthe misaligned wafers. If

costmay be 1,000 fold tocorrect it. This drastic costincreaseincludespackaging,

shipping and installation of each systemthat thefaultresided

in,

plus the cost of on-site modification and trouble shootingby

field engineers.SoftwarePrototype Hardware Prototype ClinicalEvaluation Field Operation

TypicalCurve

StateofDesign

Figure 2 Relative Costof

Repairing

aProductDuring

Life CycleAteach progressivestage, the relative cost ofrepairing a product

The remaining

issue,

time, also relates tocostbecause ofthe time incurredby

engineering and marketing departments

during

productdevelopment.However,

more specific to testability is the time spentindeveloping

the test hardware and software.Assuredly

there willbe some finite time, but this timecan beminimizedby

consideringand

implementing

testabilityduring

the initial design stages.8 Inrecent

history,

testability hastypically been implemented asan afterthought. This is represented

by

thesolid line ofFigure

3,

which corresponds to a stepfunction at each stage of productdevelopment. Each stage ofthedesignrequiresthe generation of new testvectors. For

example,iffinal product testingis notthoughtof

during

the initial design stages, simplemacrosare written to test

during

the first software prototype . This is followedby

thegeneration of new test vectors atthe firsthardware prototype, with yet another set

generatedforfield service engineers to test thefinal product at a customer's location. In

all, four separate sets oftest vectors may be generated. The desire of

designing

fortestability7

(DFT)

is to implement the generation oftestvectors and special teststructures atthe earliest stages ofthe design. The dashed line ofFigure 3 represents the

optimal time required togenerate testvectors. This is where most ofthe test vectors are

designedat the

beginning

stages and usedthroughoutthe product's life; thusdecreasing

the total time devoted to the generation oftestpatterns. In summary, increased testability

should increase thereliability while

decreasing

productlife cycle costsby

catchingfaultsat earlierdesign stages. The totaltime devotedto testing should alsodecrease

by

incorporating

testability features intotheearlyproductdesign stagesrather than ad hocSoftware Prototype

Hardware Prototype

Clinical Evaluation

J Field Operation

Typical Time

Optimal Time

>

State ofDesign

Figure 3 Total Time Requiredto Generate TestPatterns. The

amountoftimespent on testingcan beappliedto laterstages, thus

optimizing the total timespent on test.

1.2

How

Testability

Has

Been

Implemented

The definition oftestability and its impactson market needs has been presented. How

then istestability implemented? The next section examinesthe implementationof

1.2.1

Fault Types

When a testperformedon adigital design

fails,

the source is alwaysofaphysical nature.Often thesephysical faults aremappedinto logical faults forclassification and toreduce

theircomplexity. Twotypical examples ofhowcommon physical faults map intothe

logical domain are shown in Figure 4. The structuralfaultofashort circuit between two

linesoftracemay drive anode toa given voltage level. For

instance,

ifthe short occursbetween VCC and a node, VCC drives the signal high andit is labeled alogical

"stuck-at-one"

(SA1) fault. If, onthe other

hand,

GND drives thenode, then it is labeledalogical "stuck-at-zero"

(SAO) fault. Ifthefault is due to an open circuit ratherthen a

shortcircuit, power voltagesmay still drive theresultant nodes,orthey may become a

function ofthe connected signals. In eithercase, the resultofusing logical mappings to

classify faults greatly reducesthe complexity ofthe remainingfaultequations. Test

equations are difficultto determine forall buttrivial designs because ICpackaging hides

most nodes ofinterest. This leadsto the question ofhow the

faulty

internal nodesof anIC are

indirectly

monitored throughexternal pins.o

NODE 2 (short toVCC)

LKr-^.^^

OUT=/A+ ABB

NODE 1 (open circuit)

Figure 4 Circuit Example ofLogical Faults. Physicalstuck-at-faults

1.2.2

Two Requirements

ofFault

Detection

Two important conceptsoftestability are thepropertiesofcontrollability and

observability. Inorder to isolate an internalnodein a

design,

the node must have both oftheseproperties at the same time.

Specifically,

there must exist a set oftestvectors thatwhen applied to the primary inputs

(e.g.,

IC pins, PCB testpins) will isolate all thepossible faults

(controllable)

forthatnode.9Thelogic states oftheinternal node mustbe

able to propagate to a visibleoutput(observable). Ifeitherofthesepropertiesdo not

exist for agiven

fault,

then thefault is not detectable. Forexample, to testnode one(referring

toFigure4)

fora SAOfault, apply the vectorA=l,

B=l. Iftheoutput is0,

andsingle stuck-at-faultsare assumed,then node one is SAO.

Similarly,

totestnode one fora SA1 faultthevector

A=0,

B=l can beapplied. Iftheoutput is1,

then node one is SA1.Because nodeone is controllablefrom inputs A and B and observable at the outputnode

forthe SAO and SA1

faults,

it isfully

testable. One the otherhand,

nodetwo can notbetested fora SA1 fault. In orderto do so, the vectorA=0, B=0is

desired,

butthe outputfor this is the same as the output forA=0, B=l (i.e., the stuck-at-faultcase). Although

the fault is controllable, it is not observable, and hence nottestable. It is importantto

note thatwhile high numbersfor controllabilityand observability data sets are

desirable,

it is the intersection ofthe two sets thatprovides insight asto adesign's testability.10

This intersection is dependent upon system

design,

and as the previous circuit (Figure 4)shows, it is not hard to design a circuitthatis difficult to test.

1.2.3

A

Classical Example

Aclassic example ofthe implementation of

testability

over thepastdecade uses abed-of-nails approach. The

"bed"

consistsof a matrix ofprobes that applies and receives

voltage signals froma DUT (Device UnderTest).

By

abuttingthe bed-of-nails against aPCB and applying a set of parallel testvectors, the board'sresponse isrecordedand

compared to the desiredoutput. Theprobes ofthe bedcontact eitherICcomponent pins

ortest-points embedded intothe board layers asdesigned toincrease its testability. This

approach has beenfueled

by

through hole technologycomponents with typical pinspacingon 100 mil centers11

andhas performed well in

detecting

faults. One significantfeature is the ability todiagnose multiple faults withone pass ofthe overthe testhead.12

It is also able todetect shorts before

initially

powering up theboard,

preventing thepotentially catastrophic damage due to shortsbetween power and ground. Another

benefit is the ability to test and detect analogrelated faultsofhybrid PCBs. Allofthese

benefits are greatly enhanced through the use software tailored to generating testvectors,

storingthe DUT's responses to test headpasses, and.analyzing theresultsforpossible

1.3

Limits

ofClassic Example

The bed-of-nails approachhas provided a great serviceto test-engineers in thepast.

With the

increasing

complexityofICs andincreasing

PCB density, bed-of-nails testingon currentPCBs is fast approachingobsolescence. An alternative approach usingthe I/O

boundary

ofICsto shiftin testvectors througha standard testbus (IEEE 1149.1)

issuggested.

1.3.1

Increasing Density

ofICs

Among

thelimiting

factors ofthe bed-of-nails methodologyis the everincreasing density

ofintegratedcircuits.

Currently,

sub one micron technologies are producingcircuits withdensities soaringabove the classic VLSI definitionof5,000 to 50,000transistors and

requiring new definitionsofSuper Large ScaleIntegration

(SLSI)

50,000-100,000transistors andUltra Large Scale Integration

(ULSI)

forgreaterthan 100,000 transistors.Pointin fact, one recentdesign of a microprocessorcontainsover 3 million transistors!

]-The

difficulty

with thisincreased IC complexityis the sheer number ofinternal nodesthatrequire testability access coupled with the growing gate to pin ratio (Figure 5).

Becausethe growth in the numberof gates has notbeen paralleled with a growth in IC

pins, internal circuit nodeshave been even moredifficult to observe and control from the

outside. If theissue of

increasing

complexity ofVLSI circuitsdoes notlimit bed-of-nailsaccess from external nodes,itwill certainly make testingmore costly to

develop

Gate

to

Pin

Ratio

/N

Trend

Recent Past

Present

Future Trends

Time

Figure 5 Recent Trends in Gate-to-Pin Ratio. The recenttrendin

gate-to-pin-count ratio willcontinue in thefuture. This is one challenge

facedwhen testing digital circuits.

1.3.2

Increasing Density

ofPCBs

Along

with the growth in ICcomplexity, PCBs have also been subjectto increasedcomplexity. Therecent surge in PCB

density

has fueled the emergence of SurfaceMount

Technology

(SMT) components, MCM and multi-layeredboards.Unfortunately

formost bed-of-nails testing stations, each technology has introduced a new setof

challenges.

First,

most bed-of-nailstesters were built with probes suited for 100 mil DIP(Dual In-line Package) centers, not 25 and 50 mil SMTcenters.5*1*

The use ofSMT has

decreased thedegree towhich aprobe can isolate a signal.

Adding

to thisdifficulty

isstacking twobed-of-nails testers back to back. Although this is

being

done, it is themanifestation of anengineer's nightmare. Use ofMCMsthat limit tracelines between

components

by

"piggy-backing"

ICchips also limit the board's testability ofthese

components whenperformed throughexternalnodes alone. Multi-layered boards have

added the ability to create a network ofsignals as neverbefore possible. Thisis at the

expense ofadding many layers ofsignals hidden fromthe tester's probes. The

technologydriven increase in PCB densities has increasedthecost and time associated

withthe testingofsuch devices yet even higher.

1.3.3

Physical Interface

withBed-of-Nails

Another

issue,

one that relatesto the smaller IC pin spacing with SMTcomponents, isthe IC pin to bed-of-nails interface. Because ofthe decrease in pin size, there is an

increased probability of misregistration ofthe bed-of-nails interface. The misregistration

would invalidate the test results, whilecreating the potential of

damaging

the PCB existsby driving

output pinsto an undesired state.5There isalso the chance ofshorting two

pins togetherwith probesfrom the bed-of-nails thatwould again invalidate testresults. In

summary, the

increasing density

ofICs and PCBs have caused the costoftestability witha bed-of-nails testing approach to rise.

1.4

Boundary

Scan Alternative

While trying to maintainthe costofassociated with increased testability, thephilosophy

of

designing

fortestbecame prominentin the late 1980's. Themain focus ofDFT hasbeen to incorporatetestability in theearliestofdesign stages, thus minimizing itsoverall

cost. In

doing

so, a balance is soughtbetween thecostofimplementing

testability andthe cost savings thatit brings. This fosteredthe creation of several programs such as

SCOAP (Sandia

Controllability/Observability

Analysis Program)14, COMET(Controllability

andObservability

Measure forTest)9 andPREDICT (ProbabilisticEstimation ofDigitalCircuitTestability)15

toattempt toquantify testability in terms of

the DUT's observability and controllability characteristics. The problemgenerally

associated with these programs is that it is difficultto decide whatdesign modifications

are necessary tomaintain testability while minimizing itscost. Several attempts at

increasing

testability have been made. Most have been adhoc,depending

upon thedesigner. Some examples include selective insertionoftest points, partitioning larger

circuitsinto smaller blocks and usingredundant logic. Although the methods work to a

degree, there aretradeoffs intrinsic toeach choice and the major

difficulty

ofincompatibility

amongvendors. In 1985, the JTAG (JointTest ActionGroup)

gatheredtogetherto discuss the limitsofcurrenttesting strategies and

develop

a common platformto build from. Theirwork resulted in a standard based upon the use of

boundary

scan1.4.1

The Basics

The essential

boundary

scan cell is shownin Figure 6. Each cell contains aclockedregister controlledthrough an inputmultiplexerand observed through an output

multiplexer. Because ofthis clocking, the

boundary

scan cellis oftencalled aboundary

scan register (BSR). Inputdataenters fromeither thenormal input signal ortheTest

Data Input (TDI) signaland then output dataexits from eitherthe normal outputsignal or

the Test Data Out

(TDO)

signal, as controlledby

theirrespective multiplexers. The placement of scan cells along the"boundary" ratherthan at each controllingor controllednode is whatdistinguishes

boundary

scannable systems from full scan systems. Although the JTAG committee chose a novelidea,

it was not new. What was new, was thesuggestion

by

the committeeto useboundary

scan cells asthe cornerstone of atestability bus standard.16'17Tfi

(Test Data Out tonext cell)

NDlCI> (Normal Data In)

TDlO

(Test Data In

from previouscell)

NDO

O

(Normal Data

Out)

G

0

ShiftDR ClockDR

0

ModeSelect

Figure 6

Boundary

Scan Cell. The basicI/O cell usedtoseriallyshift test and normal datainto and out ofthe register.

By

linking

the functional inputand output pins of an IC together, a serial shift registerisformed.

Shifting

of serial data intoand out ofthe DUT occursthrough a pair ofI/O pins.This is analogous to applying and monitoring voltages through probes physical

contacting the ICspins.

Extending

this principle froma single IC to several on a PCBresults in increased testability through atest bus. This busconnects

boundary

scannableICs in a serialdatapath as shown in Figure 7. The added testability is not without

penalty. ExtraIC pins and PCB signals are now dedicated totest, and additional silicon

isrequired aswell. The extra silicon area or"real

estate"

is proportional tothe total

number ofICpins plus the extradesired testingfunctions. Thisthesis will present

severalfactors used to quantify the cost associated with adding

boundary

scancompatibilityto digital designs. Alsopresented will be severalexampledesigns using

is used in some oftheexamples as it is oneofthefirst ICs manufacturedto the IEEE

1 149.1

boundary

scan specifications.4The specification forthe latch is in Appendix E.

Some

boundary

scannable circuits offer powerful testfeatures thatare also explored.Moreoversince the design oftest

functionality

is on silicon, itcan be transparentto thenormal circuit operation.

TDI -* TDO-*

\

\

Printed Circuit Board

I/O Signal

Key

>- Scan Path

Figure 7

Boundary

Scan Path on PCB. This extends theboundary

1.4.2

Overcoming Density

ofICs

The

boundary

scan architecture's addressto the issue ofincreasing

circuitdensity

occurson two

fronts,

silicondesign andflexibility. The use of silicon allowstesting features togrow as the technology grows. The JTAG/IEEE 1 149.1 specifications alsoleave room

forthat growth. For example,the current standard specifiesthat the

boundary

mustbescannable, butto increase testability severalfunctions can be added to the scan path. The

use oftest methodologies such asBIST (Built In Self

Test),

PRPG (Pseudo-RandomPattern

Generator),

and PSA (Parallel SignatureAnalyzer)

can all be used toenhancetestability. These methodologies can contribute to the testing of an IC

by

eithergeneratingrandom inputvectors orcompressing output vectors intoone unique

"signature."

The design ofthese test structuresis concurrent and transparent to the

normal operation ofthe ICor PCB

being

designed. Oneexcellent example of such a teststructure is the use ofBIST19 that initiates from a theJTAG/1 149.1 testbus and takes

place within the

boundary

scan architecture. ABIST is an extension ofthe DFTphilosophy where testing

functionality

is built into the design itself. The testtypicallyconsists of afeedback systemthat generates testvectors and a similar systemthat collects

the resultsfrom the vectors. Although a BISTruns

independently

ofboundary

scan tests,the JTAG/1 149.1 specifications can provide alink into the

initializing

andrunning ofit.1.4.3

Overcoming Density

ofPCBs

andPhysical

Interface

Because

boundary

scan is developed within theIC,

it is independent ofthe shrinkingpineffects that have plagued bed-of-nails approaches. The use ofSMT and MCM

components does not degrade the testing ability nordoes it increase the cost oftesting

"silicon nail"12

is applied to

boundary

scan devices thatcan escape theuse ofa physicalprobe.

Similarly,

placingcomponentsoneither sideofthePCB orusing multi-layeredboards makes no negative impact on

testability

ofboundary

scan devices since the interconnectsofboundary

scan devices are testable, and theboundary

scan path can linktogether ICs on the PCB.20 Although powermustnow be appliedtoa

DUT,

thephysicalinterface between the DUTand the testeris limited to the testpins. The limit minimizes

thephysical interface problems and usually makes them negligible.

1.5

Problem

Statement

Thisthesis serves adual purpose. First, it facilitates theexploration of

boundary

scan devices with tools that are available atthe facilitiesin the center for Microelectronicand ComputerEngineering

atRIT.Secondly

it allowsone to gainfamiliarity

withTektronix's powerful testing tool, the LV500,currently located in the Microelectronic

Engineering

test facility.This thesis accomplishes both ofthese goals

by incorporating

the LV500 as a general testtool in the study of example

boundary

scan digital designs. Three example circuits areused to provide a betterunderstanding ofthe function of

boundary

scan cells and theJTAG/1 149.1 standard. The firstexample circuit, consisting of asingle TI '8373,

explores the BYPASS and SAMPLEoperations using theLV500. This example also shows that

boundary

scan operations run transparentto normal circuitoperations. Thesecondexample, which has a state machine designed with aTI

'8373,

shows the value ofboundary

scanindebugging

the combinational logic. The final example steps throughthe design ofa

boundary

scannable statemachine. This example, and thediscussion thatfollows

it,

provide methods ofdetermining

the cost ofadditionalboundary

scantestability. The costtradeoffs areoften themost

intimidating

hurdle for engineerstocrosswhen

deciding

ifboundary

scancompatibility is worth theeffort. In choosingtoexplore both

boundary

scan and theLV500,

my hope isto be straight forward with themost current issues and methodologies.

1.6

System Constraints

The LV500 is used primarily in

industry

forASIC (Application SpecificIC)

verification.It hasthe capabilityofgeneratingand analyzing testvectorsfor upto 256channels at

speedsup to 50 MHz. It can also monitorandplottheresults of twodimensional

parametermodifications. It is importantto note that thechoice oftheLV500 was based

upon its availability in RIT's test lab and its raw capability tocomplete the testing that

was required. The use ofthe LV500 in this thesis is limitedto the generation oftest

vectors forsimpledigital logic systems and the generation of

boundary

scan controllinglogic for testing that digital system. Notintended solely as a

boundary

scan tester, theLV500 sends out test vectors thatare

boundary

scan compatible. As itspowergoesfarbeyond what this thesis has usedit

for,

it is an excellent tool tobecome familiar with anda valuable assetto the repertoire oftesting tools in RIT's laboratory. Thetutorial circuits

ofthis lab provide are also a stepping stone in the exploring the fullpotential ofthe

LV500.

The choice ofusing TI components wasmade because oftheir

boundary

scan capabilityand theirstrong presence in this market niche. The components, used in the tutorial

circuits provided with this thesis, are also astepping stone in exploring

boundary

scannable systems. The enclosed schematics are intended forthetest-board maintenance

1.7

Terminology

There may be many new terms andideaspresented to thereaderofthis thesis. The

following

sections provide additional detail to the JTAG/IEEE 1149.1 specifications andtheTektronix's LV500 digital tester. A glossary ofterms usedis found at the frontofthe

thesis textproceeding the firstchapter.

1.7.1

JTAG Specification

In 1985 Phillips initiated the European Test Action

Group

(ETAG) topromote atestingstandardfor ICs. The group expanded intothe Joint Test Action

Group

(JTAG)

whennon-European companies such as Texas Instruments and Motorolaparticipated. At the

same timetheIEEE was

forming

its own proposal fora test bus standard. The twoorganizations collaborated and formed theIEEE PI 149.1 proposal thatwas

formally

accepted in

February

of 1990.Officially

called the IEEE 1 149.1 standard, itis oftenreferred to as theJTAG standard because of theJoint Test ActionGroup's involvement.

The goal ofthe specificationsis to allow

diversity

whilemaintaining compatibility withotherdevices. The IEEE 1 149.1 standard specifies the physical structure ofthe testbus

and how it can be interconnected to a chip. It alsodescribestheprotocol associated with

the test bus. The fourmain test signals associated with the bus are:

TDI (TestData

In)

Allowsthe inputofdata andtesting instructions fortheIC.

TDO (Test Data

Out)

Allows thedataand/or instructionsto be shifted outofthe IC.

TMS (TestMode

Select)

Controls thecurrent state oftheTAP (Test Access Port). The TAP is the state machine behind the operationofthe testingfunctions.

TCK (Test

Clock)

Clocks the inputto theboundary

scan device in on therising edge ofTCK and resultantdata outon the

falling

edge.These signals are used on the

boundary

scan architecture^!ofFigure 8. The TCK and

TMS signals are used

directly

to drive the TAP, which in turn controls the Instruction Register (IR), Data Register(DR)

and various multiplexers forthe I/O testdata. The IR data may either be shifted outthrough TDO or used as an address fora DRcommand.The figure shows a test input (TDI) entering either the IR orthe DR and shifting through

the BSRand device logic (LOGIC). The datathen travels out ofthe device throughthe

normal output pins orthrough TDO. Note that all the testing circuitry isin parallel with the normaldevice circuitry, which allows the two functions to perform without

NDI I >

(Normal

Data In)

TDI

D

(Test Data In

TCK TMS

TDO

feSR

CHIP LOGICTDI

TAP

DR

*

1

IR

TDI

BSR

TDO

-CZ>NDO

(Normal Data

Out)

4f

CZ>TDO

(Test Data Out)

Figure 8

Boundary

Scan Architecture. This isa high level diagramofthe

boundary

scan logicusedindesigning

aboundary

scan device.Figure9 containsthe TAP statediagram thatcontrols themode ofthe

boundary

scandevice. Operation includesthe

loading

of aninstruction into theIR on theright handside ofthe state machine and the shifting ofdata intothe DRon theleft hand side.

TMS=1

Q

Test-Logic-Reset TMS=0Ttms=o

cr

TMS=1 Select-DR-Scan!TMS=0

!_

TMS=1 Select-IR-Scan TMS=1 Capture-DR TMS=1 |tms=o TMS=1 TMS=0 Shitt-DR |TMS=1D

Exit1-DR |TMS=0 |tms=oCapture-1 R

TMS=1 Pause-DR TMS=0 |TMS=1 TMS=0

D

Exit2-DR |TMS=1 Update-DR TMS=1i

"Fms=o

TMS=1 TMS=0 Shift-IR |tms=iD

ExitMR |TMS=0 Pause-IR TMS=0i

TMS=0D

MS=1 Exit2-IR |TMS=1Update-1 R

TMS=1

1

TMS=0

The IEEE 1149.1 specificationslistthe functions that standard

boundary

scandevicesmust be capable ofperforming, as well as functions defined as extended. The

boundary

scannableTI '8373 chip contains someofthese extended or

"suggested"

JTAG

specifications.

Specifically,

the '8373 implements a PRPG thatprovidestest vectors forapplication to the DUTand aPSA tocompress theresultant test data intoa signature.

Faulted componentsmay be identified

by

comparing theirsignature to the expectedsignature for a

functionally

correctDUT.The '8373 is anexample that shows how scan circuitrycan be addedto a circuitdesign to

increase its testability. The additional circuitry is

fully

transparentand its testingcapabilityrequires only a four bit wide bus.

Furthermore,

theboundary

scan path neednot stop at oneIC or one PCB; it may be extended to several boards

by

simplycontinuing the scan path. Thus, the four bit testbus facilitates selfdiagnostics as well as

1.7.2

Tektronix

LV500

The TektronixLogic Verifier

(LV)

is used to testcomplicated circuitdesigns. Thecurrent system at RIT canhandle upto 64 bi-directional signals, driven

by

up to fourindependentclocks. The LV500 is primarily usedfortesting digitalcircuits and hasbeen

modified at RIT

by

the addition ofa40-pin Zero InputForce (ZIF) testhead. Althoughat higherfrequencies the testheadcan be adisadvantage

by

adding capacitance andresistance to the connection between the tester and

DUT,

the systemis adequate for theoperating speed of most normal student projects. With this testhead, any IC

directly

interfaces to the

LV500,

as thefollowing

tutorialdemonstrates. Anotherfeature oftheLV500is its compatibility with the MentorGraphicsEDA (Electronic Design

Analysis)

tools used in RIT's VLSI Design Laboratory. The application programTekWAVES can

be used to translate-2 Mentor Graphics'

test vector (event

driven)

format intothe LV500'sstatedriven format*.

Thus, one may design and simulate an IC using Mentor

Graphics'

tools, fabricate that IC

with the aid ofRIT's Microelectronics

facilities,

and then test the circuit using the sametest simulation vectors that were used in thedesign on theHP/Apollo workstations.

*

TekWAVESsamplesthe event state changesfrom the Mentorstatefileand creates an outputfilethai

2,0

Functional

Specifications

The LV500'smenus are discussed astheyrelate to the exploration of

boundary

scandevices. The firsttwoexamplesofChapter 3 utilize theconcepts presented in this

section.

2.1

Overview

ofTutorial

The organization ofthetutorial sectionsofChapter 3 is similarto a user's manual. The

format foreach ofthe examplesincludes:

1. Overview ofTest Purpose A Textual description of what the test will show

with supporting logic diagrams.

2. Test

Setup

The steps used to recall stored test parameters on theLV500.3. DUT

Wiring

Hardware and Menu A stepwise installationguide to wiringthe testheadcircuitry.

4. LV500

Setup

Menu The logical mapping oftest vectorfile signals to DUTpins.

5. Pattern test Vectors A

listing

ofthe test vectors to applyto theDUT.6.

Invoking

the test describes how to start and proceed through a test.2.2

LV500

Setup

andConfiguration

This section describes menuinformation that is displayed onthe LV500 andis pertinent

to the testing examples. The installation ofthe testhead is alsodiscussed.

2.2.1

Menus

The LV500 is driven

by

interactive menus.Physically,

thesemenus are controlledby

thekeyboard shown in Figure 10. It is divided into the

following

main groupsofkeys:1. A QWERTY (standard style) keyboard.

2. The program-controlled function keys

(top

row: FlF8)

whose functionschange accordingto thecurrent menu.

3. A dedicated function keys (alsoon the toprow: <Notes>, <>, <Print>, and

<SelectMenu>).

4. The

display

control keys(including

thejoystick),

which provide cursorlis

Sjsis

(A sE

ic2 o

~i IS 5 1

IS .. - fe-5 o og SB | 2 Q UJ -J ^w o> ccUJ H* z oz oo E=> Oil O oc a otitis _

m o <0 ffi -_C

^ . g

JC O S 3

h- o ^. n co o

i8S O Q.O

nb

ii

>li

HI

0-<

Si

4 _

IT

- 2 o t 8 itsM

2S (A > OUJ UJ* o2 So Sz Qd u. a>2 (2 S

3 C

5u

o

WCA~ 2 5 =

o E-8 2 c E.2 (A w O > tn

is

IPS

Ilc-i

<53 a < a > UJ * 5-S? $8 2 uFieure 10 LV500 Keyboard. LV500 Keyboard layoutanddescription

ofstandardfunctions.

When thedevice is

initially

turnedon, the Power Up* menu ofFigure 1 1 isdisplayed,

providing information about the system configuration. Bepatient, ittakes approximately

three minutes to

fully

powerup the system. Appendix Cdiscusses howto acquire screendumps and textfiles from theLV500. Several othermenus will beencountered

throughout this tutorial; tosee thempress the<SelectMenu>key.

They

are categorized(as shown in Figure

12)

underfour headings:1. LV

Setup

Allowsthe specification ofsupply voltages, channel assignments,et cetera priorto therunning of a test.

2.

Display

Allows theediting oftest patterns, control ofthedisplay, and theviewingoftestdata &results.

3. Utilities Allows the access of system-level tools.

4. Applications Provides access to application software packages.

Thereare three ways to move about the menus oftheLV500. Onemethod is to usethe

joystickor cursor control keys to position the highlightedcursor ontop ofthe desired

menu. Press <Return>, and the highlighted menu will open. The second methodof

transversing the menus requires thepressing ofafunction

key

(F4 through F8). As Figure 12 shows, there are four function keys corresponding to the fourmenu categories.This will open the menu that is highlighted fora particularcategory. The third

possibility is tohit the <Select Menu>

key

while in the main menu. This allowsforthename ofa specific menu to be entered. In a submenu, the <SelectMenu>

key

can beused to return back tothe main menu.

LU 5S0 9'JrE,4-l TEKTROHi:-: LU 501-3

Utilities Power Up Idle

?-,-11

slot 0 Controller PASS

slot 1 Memory S Mbyte PASS

slot o 9LhN Network Controller PASS

slot 3

slot 4 95'164PM 64 Channels'Pattern Generation pass slot 5 9S')64E 64 Channels'Error Storage PASS slot 6

slot 77 slot 3

Mainframe PASS Floppy Disk Hard Disk

1.?. Mbyte 43 MByte

PhSS PhSS

System Software Release Version 1.41 Date: 7 June 1991 Previous Shutdown: Normal Time* 13:43

Press Select Menu'

or Shift Select Menu to move between menus

Press 'Notes'

twice for a description of the LU 530 NOTES system

Fl STnrT $'Jfc4-l F4 F5 TERMINhL SET SETUP TIME

Figure 11 Power

Up

Menu. LV500 menudisplayeduponinitialsystem power up.

4-1 Utilities p. Idl*

Ui 5GG MENU SELECTION

Module

^i-Ut.4-1

LU Set.up Display Utilities Hppl ications

F4 F5 F* F7

Sy= Conf1q Pattern Power Up LU Toolkit CIue Setup Macro Save Festore

Sys Monitor Schmoo Disk Services

Symbol Edi tor

Conf13 Commumcation

DUT Uirin:i HW SU Uersion

Channel Orientation

Template

Det Schmoo

Press F4 , F5, F6 or F7 to move to the sel ected menu.

Press Select Menu or 'Shift Select Menu'

to move between menus. Press Notes twice for a description of the LU 500 NOTES system. Fl

ESCAFE

? CAMi:EL

F4 FS F6 F7 FS

MOUE TO MOUE TO MOUE TO MOUE TO EXIT LU SETUP DISPLAY UTILITY APPLICTN 5 SA"t Fieure 12 Main Selection Menu. LV500menushowingthefourmain

functionalcategories.

Open the Orientation menu atthis time. It appears undertheUtilitiescategory and

contains usefulinformation aboutthe LV500.

Also,

the<Notes>key

which provides online documentation forthecurrent cursorfield. When pressedtwice in succession, the

notes

key

describes itself. Therestofthis tutorial willprovide enough information aboutthe LV500 to step through the

boundary

scan examples. Foramore in-depth look at theLV500's

functionality

referto the appropriate Tektronix LV500manual.23'24>252.2.2

Testhead

Installation

Ifthe 40 pin ZIF testhead is not the currently installed, then it will need to be doneprior

toLV500 power up. Ifyou are notfamiliarwith the installationofthe testhead, it is wise

to ask forthe assistance of someone who is. There are gold elastomeric connectors on

the underside ofthetesthead that areeasily damaged. These gold

"contacts"

provide the

means to pass the signalsfrom the LV500 testhead to its controller. Avoid touching

them because dirt and oil from yourfingersmay degradethe electrical contacts, and

avoid pokingat them since this may break the contacts. Ifit becomes necessary toclean

the contacts, do so with a cotton swab and isopropyl alcohol, wiping gently with the

"grain"

ofthe gold wires. Figure 13 displays the 40 pinZIFtesthead installed and the

LV500'scomponents appropriately connected. Oncethe testheadis secured, power up

the LV500Tterminal and then the LV500controller. This order of powerupis preferred

LV500

Tester

40pinZIF Testhead

LV500T

LV500 Conrro ler

2.3

Figure 13 LV500 SystemConfiguration. Basic hardware setup for

communicationbetweenLV500and tutorialcircuits.

40

pinZIF Testhead

In this tutorial the 40pin ZIFtesthead will be used asthe interface between any DUT and

the LV500. Figure 14 shows the properpin-outforthe LV500 to testhead mapping.

Since theLV500 has 64 signals and the testhead has only 40 horizontalchannels, there

are 24 channels on the LV500that are not connected to the testhead.

LV500 Port Connections

Ni

VCC

GNDL

2.7

2.5 2.3

2.1

1.f

1,d

1.b

1.9

1.7

1.5

1.3

1.1

Of

O.d

O.b

0.9

0.7

0.5

0.3

0.1

40 Pin ZIF

Wiring

21

25

30

35

40

Figure 14 40 pin ZIF

Wiring

Diagram. Pin-outofthe40pinZIF3,0

Tutorial

for Test Boards

Thischaptercontains the tutorialforexploring

boundary

scannabledevices on theLV500. The use ofthree examples allows arampingoftheconcepts and aconcrete

foundation forexploring othercircuits on the LV500. The first example includesonly a

single '8373 connected to the LV500. Itdemonstrates theBYPASS command in test

modeofoperation, the BYPASS command in normal mode of operation and the

SAMPLEcommand. The second example includes a '8773 with additional

combinational logic. This example shows how

boundary

scannable ICsassist indebugging

digital designs. The third andfinal example utilizes software tools availablein RIT's VLSI

Laboratory

to shows how a circuit's testability isincreased throughboundary

scan design methods.3.1

Single Test

Chip

The single chiptest example is used tointroduce the world of

boundary

scan devices. Asingle '8373 is pluggedinto theDUTtesthead and exercised using theLV500.

3.1.1

BSCANJ

Test

Setup

Now step through theLV500's menusto verify the proper operation of a single

SN74BCT8373 IC and provide a basis from whichto furtherexamine the '8373's

functionality. In order to run a completed test, three components are needed. The

following

test components can be developed in anyorder, but theymust all be present atthe time the device is tested:

DUTWiring

A properly wired circuiton the testhead.

LV500 setup Acomplete mappingof signals from the testvector file to the

DUTand adescription ofthe timingrelationships for each testcycle.

Pattern testvectors Acomplete listofinputs

driving

the DUT and theexpected outputs.

Once the LV500 is running and the Power

Up

menu ofFigure 1 1 is successfullydisplayed, the BSCAN_I system configuration software must be loaded. This will setthe

LV500's currentworking environment. If still in the Power

Up

menu, press the <SelectMenu>

key

to enterthe main menu ofFigure 12. Now, open the Save/Restoremenuunder the Utilities category. A menu similarto the Save/Restoremenu ofFigure 15

should be displayed.

LU 500 92U64-1 Utilities a-e Pesto Idl

Opera1i on : Pestore SeKip

File! BSChN I-new

Ccwfoents! MulMchip boundary ican +'j+or1 'il C'i =pl:i-j: [ire

:t.,ry C'lil- tree =pa.:e: 3129? fbVe=

File Home Size i.cv-ed fOWien*=

743 te:-t r^ 05 09 91 00:15

74F547 c -.

03 13'94 01=15

bscmnj 71 03 10 91 04:4? 91fi|i1e :hifj boundary =: :ir. trjtor1a1.

-BSCHtl I-ne"-71

-03 07 93-09H4 Multichip boundary =ccin tutorial.

-BSCrtNJI 70 03-'

07-93 11:55 Multichip boundary =<:an tutorial. BSChM II-ne c-5 OS 07 "95 0:50 MuHi-zhip boundary scan tutorial. BSCAN III 7 03 13 91 15:15 E^ploriny the =<:an path.

HHC547 Z'c. 05 ? 94 00:46 Bill = 547 test file

HUCPEGFILE c

-05 c'9 94 08s@l Bills reyifter test file

IN"ERTEP 51 10 15-91 03:25 INi'EPTEP SCHrlOO SETUP

INUEFTEPZ 51 11 '01 91 03:30 W'EPTEP i-CHMOO SETUP KENLED

c~

04-17-94 04:49

Us$ data jcrolling ^ey= *o select file we.

Fl

START

?2>ig.4-1

FS

EI.ECUTE OFEFMTinri

Figure 15 Save/Restore Menu. LV500 Menu displayed whensaving

Set the first field

(Operation)

ofthe Save/Restoremenu to"Restore Setup"by

eitherusing the <Open/Close>

key

and thecursorarrows, orby

typing the command in.Next,

enter

"BSCANJ"

in the File field as the name ofthe file torestore. This file contains

the system setup forthe test tobe performed. It was written

interactively

ontheLV500T

by

myselfand saved on this same screen. Upon completing the above steps,press F8:EXECUTE OPERATION to execute therestore. Itonly takes afew secondsto

load the

file,

after which <SelectMain> can be pressed.40 Pin ZIF

LV500Port

/

WirinS

S : !i iurona!VCC

GND-8pin Socket

Figure 16 Testhead

Wiring

Diagram. Pin-to-40pinZIFwiringdiagram forfirst tutorial circuit.

3.1.1.1

DUT

Wiring

This isthe firstofthe three sections

describing

the testcomponents forthe DUT. Inthissection the installationand wiring ofthe '8373 ICwill beperformed. Because only one

IC is

being

used, itwill be installeddirectly

intothe 40pin ZIFtesthead. Ifthe ICis'

not

currently in the testhead then plug it

in,

conformingto Table 1 below. The IC should beinstalled such that its firstpin contacts port0.0 ofthe testhead (andthe 12th pin contacts

port 1.6). As Figure 16 shows, the IC is inserted

directly

abutting the end ofthe 40 pinZIF closestto you. Because the '8373 IC has VCC andGNDpin mappingsthat differ

from the MOSIS 40pin standard, some ofthe signals must be routedto alternative

channels.

The '8373 is an octal d-type latch when operated in normal mode of operation. The IC is

also

fully

IEEE 1 149.1 compatible when operated in its testmode. When intest mode.the normal operation ofthe octal latch is inhibited and the testcircuitry is enabled to

observeand control the device's I/O boundary. Several instructionscanbe loaded and

executed

by

using thefour standardtestlines (TDI,TDO, TCK,

TMS). In addition to thestandard features for IEEE 1 149.1 compatibility, the octal latchcan also perform

additional tests such as PRNG and PSA. The

following

commands (Appendix E containsdetailed

description)

are executedin this tutorial:EXTEST

Boundary

scan registeris selected in the scanpath. Datapreviouslyloaded into the BSR is applied to device inputs and throughdevice outputs. Device

is in test mode of operation.

BYPASS One bit bypassregisteris selected in the scan path. A logic 0 is loaded

SAMPLE

Boundary

scan registeris selected in scan path. A snapshot istaken ofthedevice inputs and outputs. The device operatesin normal mode.

Logical

Path Name

Logical

SignalName

Sector/

Channel

DUT

Pin

0 C 0.0 1

1 1Q 0.2 ">

2 2Q 0.4 3

3 3Q 0.6 4

4 4Q O.a 5

5 GND 1.2 6

6 5Q O.c 7

7 6Q O.c 8

8 7Q 1.0 9

9 8Q 2.0 10

10 TDO 1.4 11

11 TMS 1.6 12

12 TCK 1.7 13

13 TDI 2.3 14

14 8D 1.3 15

15 7D 1.1 16

16 6D O.f 17

17 VCC 1.5 18

18 5D O.d 19

19 4D 0.9 20

20 3D 0.7 21

21 2D 0.5 22

ii ID 0.3

23

23 *OC 0.1 24

Table 1 Logical

Mapping

ofDUT. Tablelisting

themapping oftheLogical Signalname withtheLV500 channelandDUTpins.

Figure

Related documents

The PROMs questionnaire used in the national programme, contains several elements; the EQ-5D measure, which forms the basis for all individual procedure

Referring back to the relation between a payment based protest attitude and SQ bias, these results suggest that without the entreaty, some choices might be governed by

We surveyed fallow vegetation and total carbon and nitrogen after swidden cultivation by Karen people in the Bago mountain range and compared with those in natural teak forests

The premium private label products had most of the package elements the respondents found to signal good quality: the dark green color, the gold (or beige in the case of

prevalence of obesity among the sampled women. The contribution of chapter three was in utilising the research objectives to investigate if nutrition transition existed in

Formic acid content of Cheddar cheeses made of full fat control (FFC); Low fat control (LFC); Low fat cheese with pectin addition (LP); low fat cheese with Novagel addition (LNG)

contacts formed only in the native (pink) or activated (green) register).. The activated Rec dimer allows formation of a catalytically competent GGDEF dimer. a) Changes in