Low-Power Programmable Prpg with Test Compression

Capabilities

P. Snigdha Kamala & Sreenath Kashyap

Assist Professor Department Of ECE Kommuri Pratap Reddy Institute of Technology, Hyderabad, Telangana, India

Abstract: This paper depicts another

programmable low power test compression strategy that allows shaping the test power envelope in a completely unsurprising, exact, and adaptable form by adapting the existing rationale BIST infrastructure. The proposed hybrid plan proficiently combines test compression with rationale BIST, where the two systems can work synergistically to convey great test. Exploratory outcomes obtained for industrial outlines show possibility of the proposed test conspire and are accounted for herein.

Keywords: Built-In Self-Test, Hybrid Low

Power Compression, Low Power Test; Test Data Compression, Scan-Based Test; Toggling.

I.INTRODUCTION

Testing accept to be a fundamental part within the field of generation. The occasion of imperfection in VLSI circuit result in testing each chip. The deformities that may happen in VLSI chips may cause outline mistakes, material imperfection, malfunctioning of gear. As the measure of VLSI chips is compressing step by step the request on power and zone use is all the more subsequently testing is obligatory. Testing can perform internally or remotely. Open air

International Journal of Research

Available at https://edupediapublications.org/journals

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue14 November 2017

The nonexclusive piece chart of a BIST is appeared in Fig. 1.BIST arrangement comprises of a few pieces given below

Circuit under Test (CUT): It is the piece of the

circuit tested in BIST mode. It can be combinational, consecutive or a memory. During testing process on CUT a genuine circuit mark is created and after that contrast through the highquality machine signature with chooses whether CUT is blemished.

Test pattern generator (TPG): This is a one of

the essential square of BIST circuit to be tested in which data analyzing and compressing has been finished. The blame that was produced from different blame that happened is an immediate capacity of test designs came about by the test design generator (TPG) and connected to the CUT. Here a Linear Feedback move enlist for the most part create designs this examples are produced in pseudo irregular mold.

Test Controller: It is the one of the main piece

in BIST framework which controls the general framework for test execution. It gives flag to control all squares. In the event that control flag is 0 then BIST goes into test mode. In the event that control flag is 1 then BIST goes into ordinary mode

Response Analyzer: It goes about as a

comparator with put away reactions. Contrasts the put away reaction and the tested yield and shows whether the chip breezes through or comes up short the test.

This paper exhibits a completely programmable low power test compression conspire that is integrated in each path with a power-mindful

pseudorandom test design generator created for BIST applications. Thus, its equipment punishment is for all intents and purposes none, as well as makes a domain that can be utilized to touch base at a productive hybrid

arrangement combining favorable circumstances of scan compression and rationale BIST

.

II. BASIC ARCHITECTURE OF PRPG

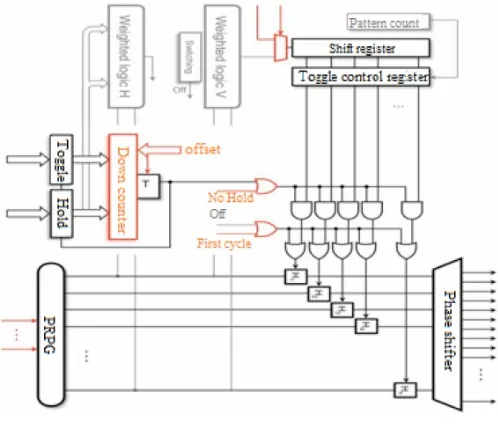

Fig 2: Low power PRPG Architecture

The control enlist is reloaded once per design with the substance of an extra move enroll. The empower signals injected into the move enlist are created in a probabilistic manner by using the ring generator and a programmable arrangement of weights (actualized by methods for weighted rationale V in Fig. 1). A 4-bit enroll Switching is utilized to initiate weighted rationale, and allows selecting a client defined level of switching movement. Straightforward rationale related with a similar enroll recognizes a code used to switch the low power usefulness off. Given just 15 switching codes, the resultant 15 diverse toggling rates may not generally be satisfactory. In this manner, a shifting time of each test design is an arrangement of alternating hold and flip intervals. A fundamental T-sort flip-slump moves thegenerator forward and backward between these two states as appeared in Fig. 2.If it is set to 0, the generator enters the hold time frame with all hooks handicapped (through AND doors)

International Journal of Research

Available at https://edupediapublications.org/journals

e-ISSN: 2348-6848 p-ISSN: 2348-795X Volume 04 Issue14 November 2017

III. LP-DECOMPRESSOR

Keeping in mind the end goal to encourage test data decompression while preserving its original usefulness, the hardware of Fig. 2 has been re architected. This is represented in Fig. 3. The center principle of the new decompressor is to impair both weighted rationale pieces (V and H) what's more, to send deterministic control data instead. Inparticular, the substance of the flip control enroll would now be able to be chosen in a deterministic way because of a multiplexer set before the input of the move enlist. Moreover, the Toggle and Hold registers are utilized to on the other hand preset a 4-bit binary down counter, and along these lines to determine urations of the hold and flip stages. At the point when this circuit achieves the estimation of zero, it makes a committed flag go high with a specific end goal to flip the T flip-slump. A similar flag allows the counter to have the input data kept in the Toggle or Hold enroll entered as the following state Both, the down counter and the T flip-flounder should be initialized each test design. The initial

estimation of the T flip-tumble chooses whether the decompressor will begin work either in the flip or in the hold mode, while the initial estimation of the counter, additionally alluded to as a counterbalance, and determines that mode's term. As can be watched, usefulness of the T flip-flops remains the same as that of the low power PRPG (see Section2) yet two cases. Most importantly, the encoding method (see Section 4) may totally incapacitate the hold stage (when all hold locks are hindered) by loading the Hold enroll with a fitting code, for instance, 0000. On the off chance that recognized (No Hold in the figure), it abrogates the yield of the T flip-tumble by using an extra OR door, as appeared in Fig. 3. Subsequently, the whole test design will be encoded within the flip mode only. Also, all hold

locks must be appropriately initialized.

Subsequently, a control flag First cycle delivered toward the finish of the ring generator initialization stage reloads all locks with the present substance of this piece of the decompressor.

Fig. 3 LP decompressor

Fig. 4LP-decompressor

V. CONCLUSION

As appeared in the paper, the recently proposed low power PRPG is fit for acting as a completely utilitarian test data decompressor with capacity to unequivocally control scan move in switching action through the way toward encoding, while its low power test rationale requires extensively littler measure of silicon land than that of the existing low power compression plans. The proposed hybrid arrangement allows one to productively combine test compression with rationale BIST, where the two methods can work synergistically to convey brilliant test. It is thusly an exceptionally alluring low power test conspire that allows for trading-off test scope, design tallies and toggling rates.

VI. REFERENCES

[1] P. Girard, L. Guiller, C. Landrault, S. Pravossoudovitch, and H.-J. Wunderlich “A modified clock scheme for a low power BIST test pattern generator,” Proc. VTS, 2001, pp. 306-311.

[2] V. Gherman, H.-J. Wunderlich, H.

Vranken, F. Hapke, M. Wittke, and M. Garbers, “Efficient pattern mapping for

deterministic logic BIST,” Proc. ITC, 2004, pp. 48–56.

[3] Michal Filipek and Nilan Mukharjee,

Grzegorz Mrugalski. “Low Power

Programmable PRPG with Test Compression Capabilities”, IEEE transactions on Very Large Scale Integration, Vol 23,no.6,june 2015.

[4] B.Singh, A. Khosia, and S. Bindra, “Power optimization of linear feedback shift register (LFSR) for low power BIST,” in Proc. IEEE Int. Adv. Comput. Conf. (IACC), Mar. 2009, pp. 311–314

[5] X.Liu and Q. Xu, “On simultaneous

shiftand capture-power reduction in linear

decompressor-based test compression

environment,” in Proc. Int. Test Conf. (ITC), Nov. 2009, pp. 1–10, paper 9.3.

[6] B. Koenemann, “LFSR-coded test

patterns for scan designs,” Proc. ETC, 1991, pp.237-242.

[7] T. Saraswathi, K. Ragini, and C. G. Reddy, “A review on power optimization of linear feedback shift register (LFSR) for low power built in self test (BIST),” in Proc. 3rd

Int. Conf. Electron. Comput.Technol.